Ethernet Based Open Network CC-Link IE Compatible Product Reference Manual

# Notice for Safety Design

(Read before using this product.)

• Mitsubishi Electric Corporation (Mitsubishi) puts the maximum effort into making its products better and more reliable, but there is always the possibility that product failure or malfunction may occur. Failure or malfunction of Mitsubishi products may lead to personal injury, fire, and/or property damage. Remember to give due consideration to safety when making your designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material, or (iii) prevention against any malfunction or mishap.

# Notes Regarding This Manual

(Read before using this product.)

- This manual is intended as a reference to assist our customers in the development of CC-Link family products best suited to the customer's application; it does not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi in relation to the technical information described herein.

- When using any or all of the information contained in this manual, including product data, technical information in diagrams and charts, programs, and algorithms, please be sure to evaluate all information not only in terms of the technical details, programs, or algorithms, but as a total system before making a final decision on the applicability of the information and products. Mitsubishi assumes no responsibility for inapplicability.

- Mitsubishi assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in this manual.

- The precautions given in this manual are concerned with this product only. For the safety precautions of the system, refer to the user's manuals for the products used.

- The model names of each components described in this manual are subject to change at the discretion of each manufacturer.

- All information contained in this manual, including product data, diagrams, charts, programs, and algorithms, represents information on products at the time of publication of this manual; the items and specifications described herein are subject to change by Mitsubishi without notice. Please consult your local Mitsubishi Electric representative for the latest product information before purchasing a Mitsubishi product.

- When disposing of a product that uses this product, treat it as industrial waste.

- The prior written approval of Mitsubishi is necessary to reprint or reproduce this manual in whole or in part.

- If you have any questions or concerns regarding the details described in this manual, consult your local Mitsubishi Electric representative.

# **Security Precautions**

• To maintain the security (confidentiality, integrity, and availability) of the system against unauthorized access, denial-of-service (DoS) attacks, computer viruses, and other cyberattacks from external devices via the network, take appropriate measures such as firewalls, virtual private networks (VPNs), and antivirus solutions.

- Mitsubishi dedicated LSI ("the PRODUCT") shall be used in conditions;

- i) where any problem, fault or failure occurring in the PRODUCT, if any, shall not lead to any major or serious accident; and

- ii) where the backup and fail-safe function are systematically or automatically provided outside of the PRODUCT for the case of any problem, fault or failure occurring in the PRODUCT.

- The PRODUCT has been designed and manufactured for the purpose of being used in general industries. MITSUBISHI

SHALL HAVE NO RESPONSIBILITY OR LIABILITY (INCLUDING, BUT NOT LIMITED TO ANY AND ALL RESPONSIBILITY OR

LIABILITY BASED ON CONTRACT, WARRANTY, TORT, PRODUCT LIABILITY) FOR ANY INJURY OR DEATH TO PERSONS

OR LOSS OR DAMAGE TO PROPERTY CAUSED BY the PRODUCT THAT ARE OPERATED OR USED IN APPLICATION NOT

INTENDED OR EXCLUDED BY INSTRUCTIONS, PRECAUTIONS, OR WARNING CONTAINED IN MITSUBISHI'S USER,

INSTRUCTION AND/OR SAFETY MANUALS, TECHNICAL BULLETINS AND GUIDELINES FOR the PRODUCT.

("Prohibited Application")

Prohibited Applications include, but not limited to, the use of the PRODUCT in;

- Nuclear Power Plants and any other power plants operated by Power companies, and/or any other cases in which the public could be affected if any problem or fault occurs in the PRODUCT.

- Railway companies or Public service purposes, and/or any other cases in which establishment of a special quality assurance system is required by the Purchaser or End User.

- Aircraft or Aerospace, Medical applications, Train equipment, transport equipment such as Elevator and Escalator, Incineration and Fuel devices, Vehicles, Manned transportation, Equipment for Recreation and Amusement, and Safety devices, handling of Nuclear or Hazardous Materials or Chemicals, Mining and Drilling, and/or other applications where there is a significant risk of injury to the public or property.

Notwithstanding the above restrictions, Mitsubishi may in its sole discretion, authorize use of the PRODUCT in one or more of the Prohibited Applications, provided that the usage of the PRODUCT is limited only for the specific applications agreed to by Mitsubishi and provided further that no special quality assurance or fail-safe, redundant or other safety features which exceed the general specifications of the PRODUCTs are required. For details, please contact the Mitsubishi representative in your region.

• Mitsubishi shall have no responsibility or liability for any problems involving system trouble caused by DoS attacks, unauthorized access, computer viruses, and other cyberattacks.

# **CONTENTS**

| Notice for Safety Design                                              | 1  |

|-----------------------------------------------------------------------|----|

| Notes Regarding This Manual                                           | 1  |

| Security Precautions                                                  | 1  |

| Conditions of Use for the Product                                     | 2  |

| CONTENTS                                                              | 3  |

| Relevant Manuals                                                      | 9  |

| Terms ·····                                                           | 10 |

| Usage Precautions                                                     | 12 |

| Address Notation                                                      | 12 |

| Radix Notation                                                        | 12 |

| CC-Link Partner Association                                           | 13 |

| 1 OVERVIEW                                                            | 15 |

|                                                                       |    |

| 1.1 Development Features                                              |    |

| 1.2 Specifications of CP520 Hardware·····                             |    |

| 1.3 Communication Specifications of CP520 Application Products        | 16 |

| 1.4 Enclosed CD-ROM·····                                              |    |

| 1.5 Sample Code Overview                                              |    |

| 1.6 System Configuration                                              |    |

| 1.7 Relationship with R-IN32M4-CL2 ······                             | 21 |

| 2 STUDYING AND PREPARING SPECIFICATIONS PRIOR TO DEVELOPMENT          | 22 |

|                                                                       |    |

| 2.1 Acquiring a MAC Address                                           |    |

| 2.2 Acquiring a Vendor Code and Selecting a Device Type               |    |

| 2.3 Arranging Components                                              |    |

| 2.4 Preparing for Hardware Development·····                           |    |

| 2.4.1 Pins connected to hardware switches                             |    |

| 2.5 Preparing for Software Development                                |    |

| 2.5.1 Software development procedure                                  |    |

| 2.6 Studying a Method for Setting a Station Number and Network Number |    |

| 2.7 Studying Assignment of Link Device Properties                     |    |

| 2.8 Studying Implementation of Hold/Clear Processing                  |    |

| 2.9 Preparing to Support Various Engineering Tool Functions           |    |

| 2.10 Preparing to Create CSP+ Files                                   |    |

| 2.11 Preparing for the Conformance Test                               |    |

| 2.11.1 Items required for the conformance test                        |    |

| 2.11.2 1000BASE-T compliance test ······                              | 31 |

| 3 FUNCTIONS OF THE CP520 APPLICATION PRODUCT                          | 32 |

| 3.1 Cyclic Transmission Function                                      |    |

| 3.2 Transient Transmission Function                                   | 34 |

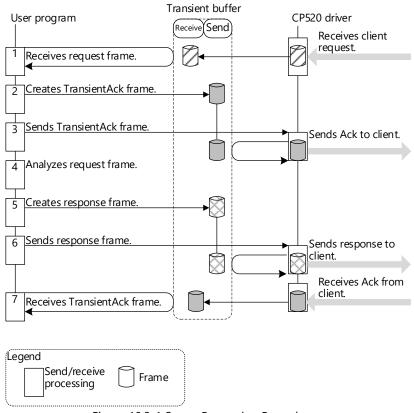

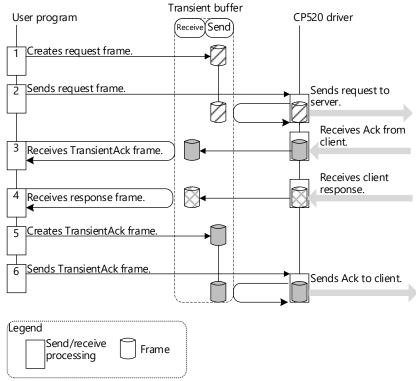

| 3.2.1 Transient transmission client and server functions              | 35 |

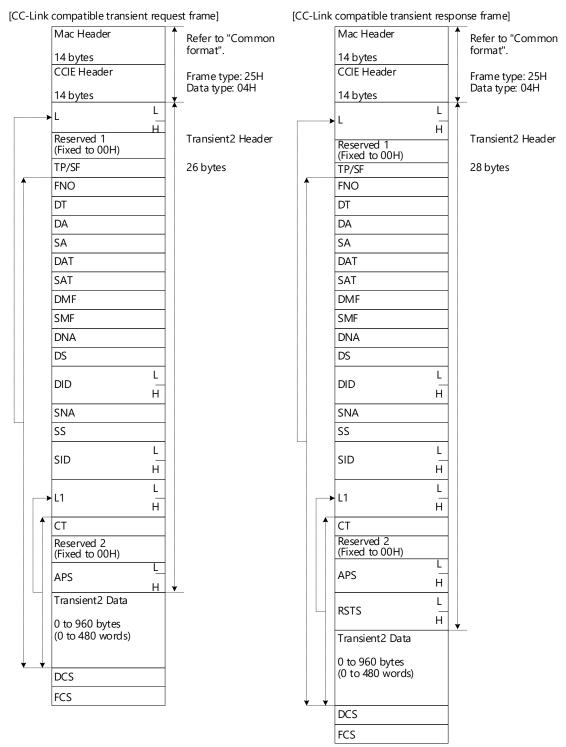

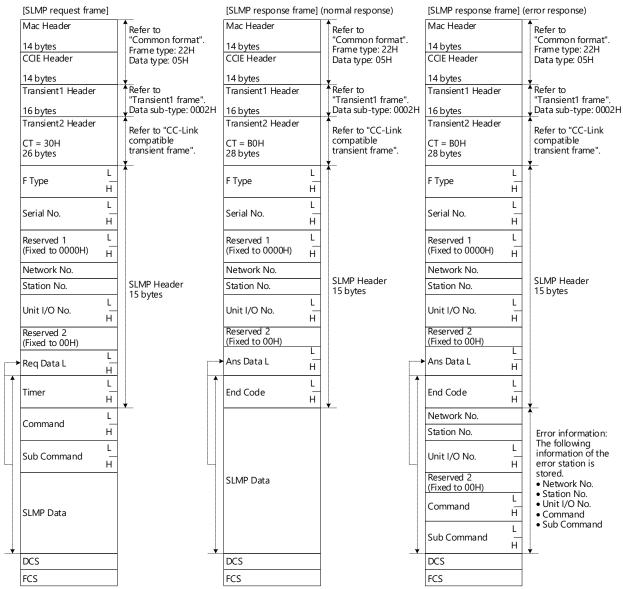

| 3.2.2 Transient transmission frames·····                              | 35 |

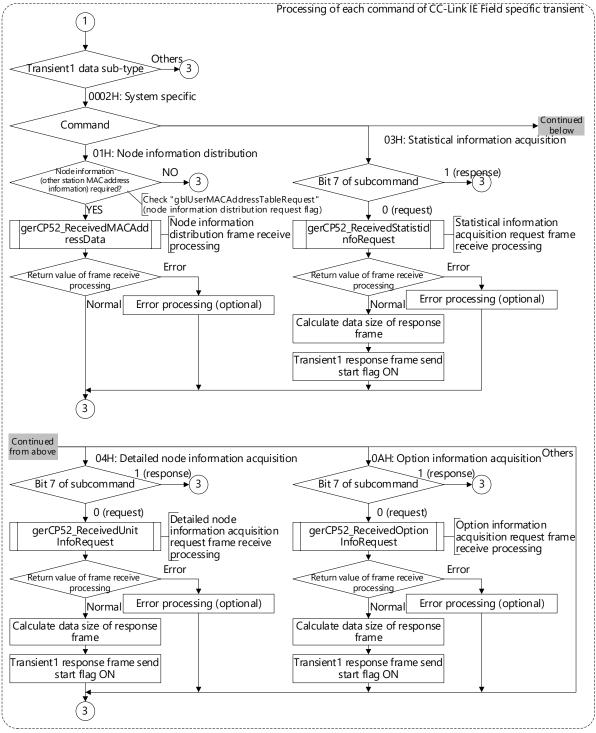

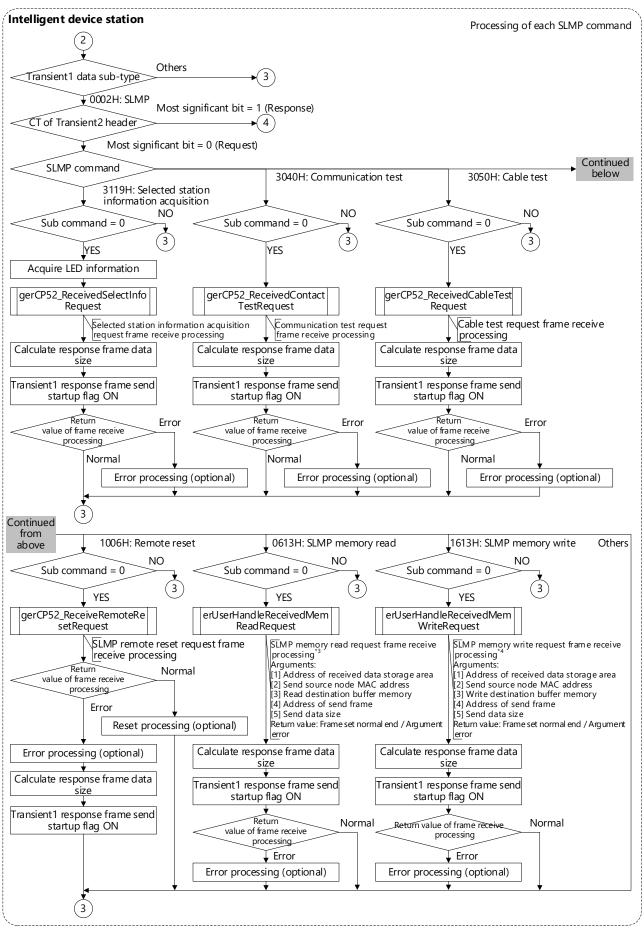

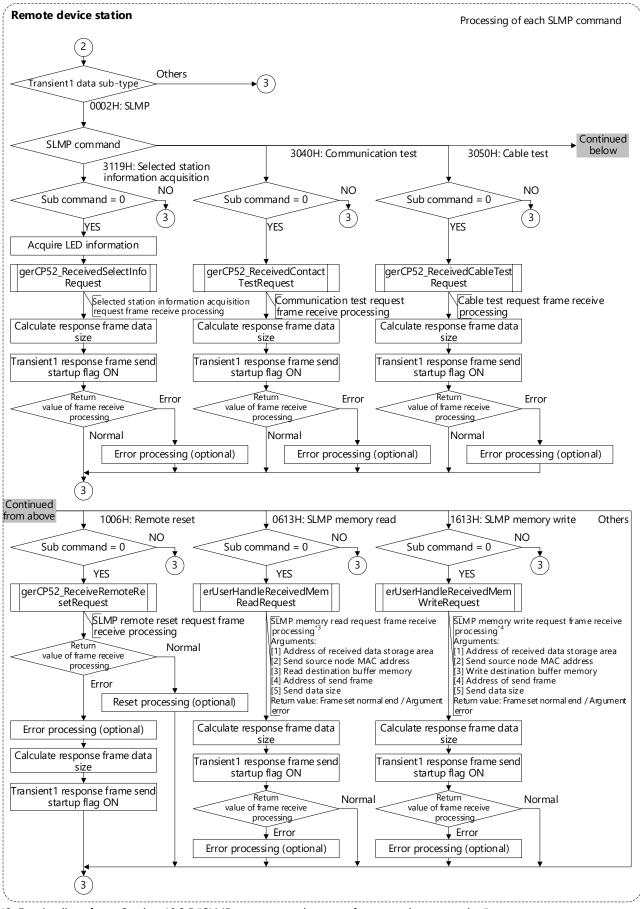

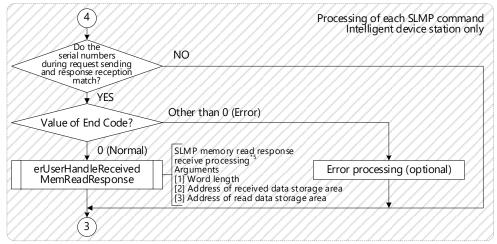

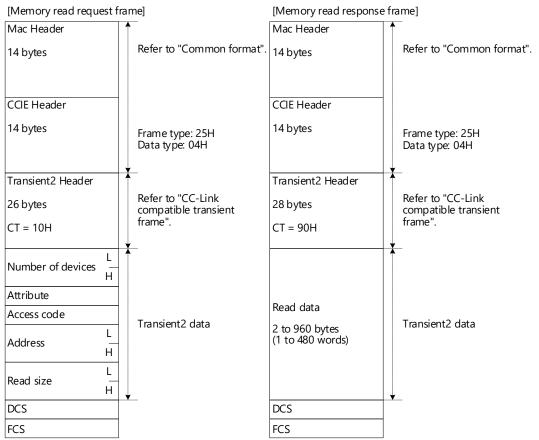

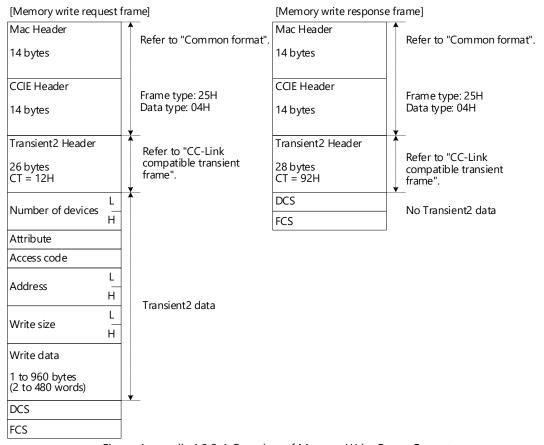

| 3.2.3 Transient transmission commands                                 | 36 |

| 3.3 MyStatus Send/Receive Function                                    | 37 |

| 3.3.1 Sending MyStatus ·····                                          |    |

| 3.3.2 Receiving MyStatus ·····                                        |    |

| 3.4 Status Display Function                                           |    |

| 3.4.1 Status display by LEDs·····                                     |    |

| 3.4.2 Controlling the LEDs ····································       |    |

| 3.4.3 Controlling USER LEDs······                                     |    |

| 3.4.4 Controlling the L ERR. LED                                      |    |

| 3.4.5 Enabling/Disabling the LED function                             |    |

| 3.5 Bypass Mode·····                                                                          | 42 |

|-----------------------------------------------------------------------------------------------|----|

| 3.6 MIB Information                                                                           |    |

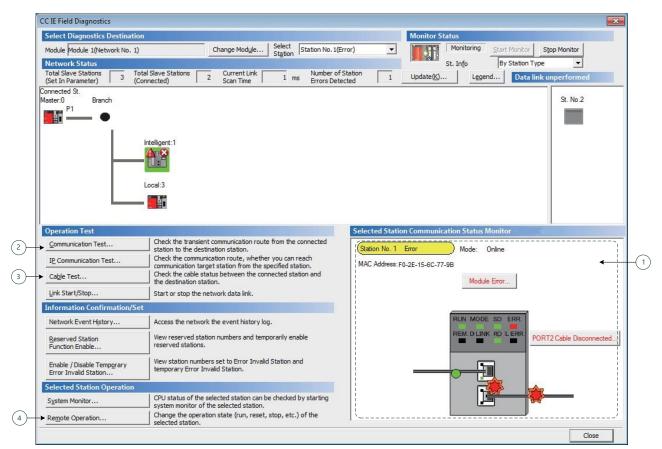

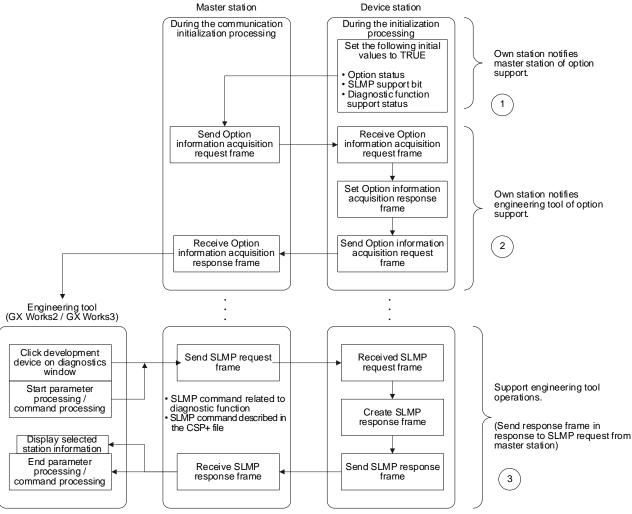

| 3.7 CC-Link IE Field Network Diagnostics                                                      | 43 |

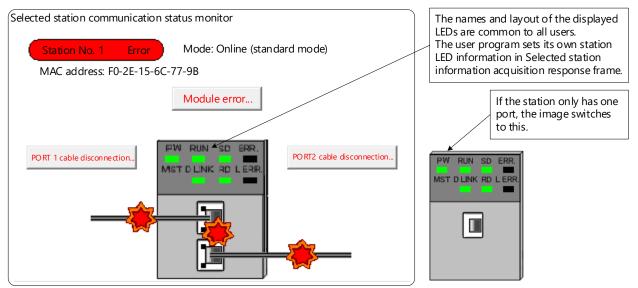

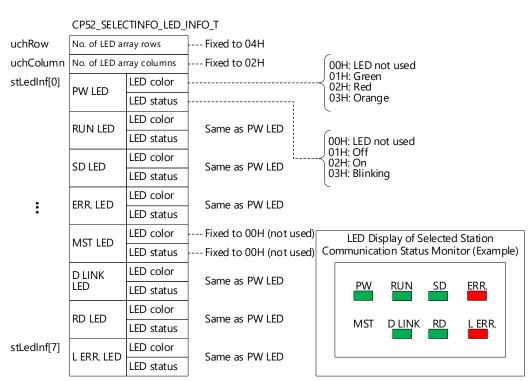

| 3.7.1 Selected station communication status monitor LEDs                                      | 44 |

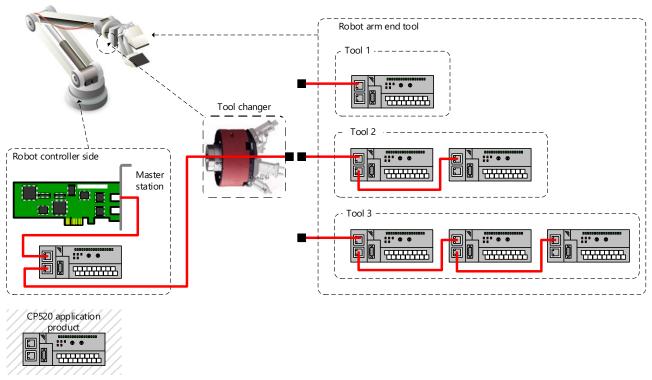

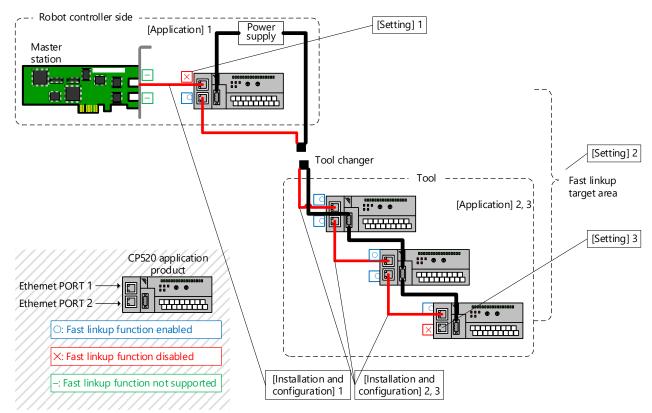

| 3.8 Fast Linkup Function                                                                      | 45 |

| 3.8.1 Fast linkup function enable/disable setting                                             | 46 |

| 3.8.2 System configuration for fast linkup                                                    |    |

| 3.8.3 Precautions for fast linkup function                                                    |    |

| •                                                                                             |    |

| 4 CP520 SPECIFICATIONS AND FUNCTION OVERVIEW                                                  | 49 |

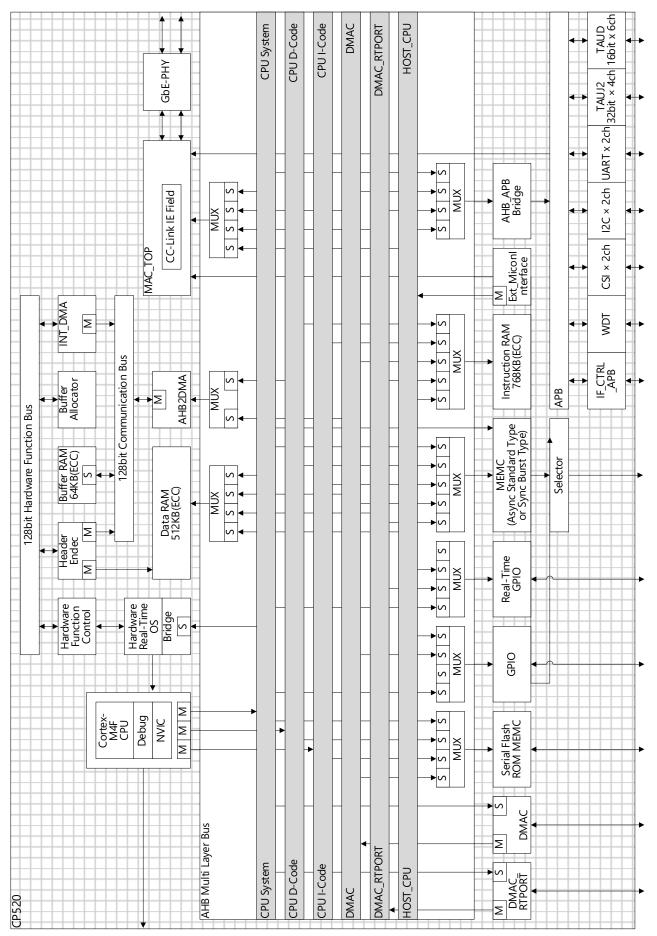

| 4.1 Function Overview                                                                         | 49 |

| 4.2 Function Block Configuration                                                              | 51 |

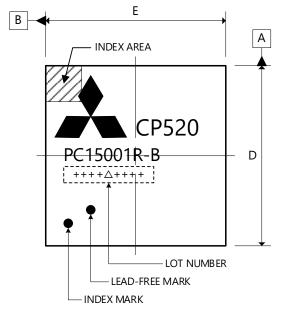

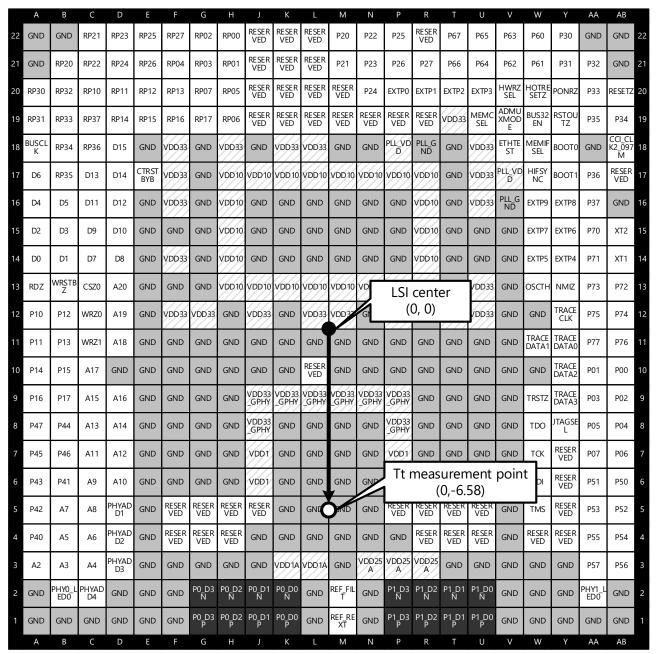

| 4.3 External Appearance                                                                       | 52 |

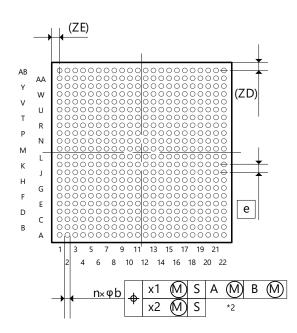

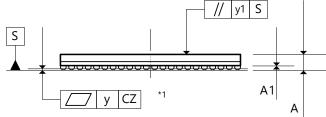

| 4.4 Pin Assignments                                                                           | 53 |

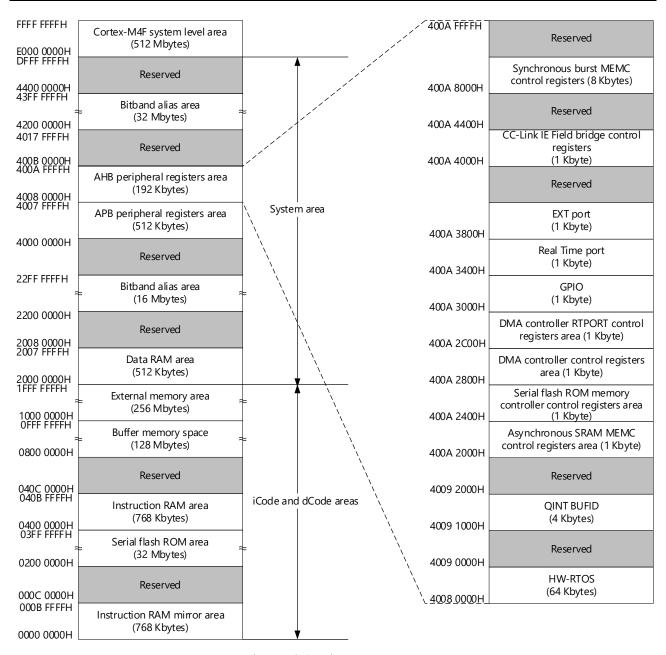

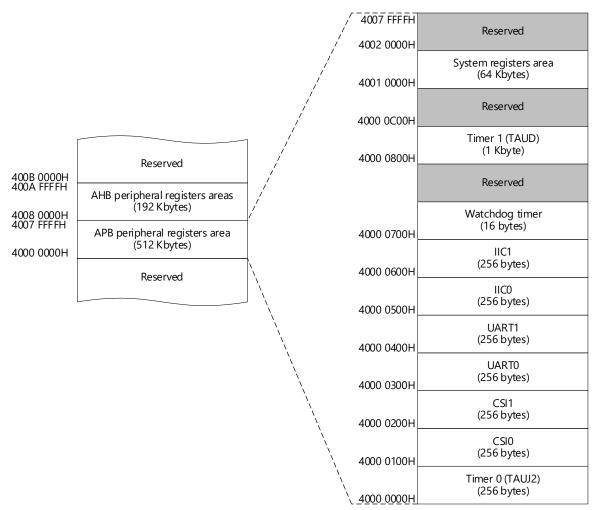

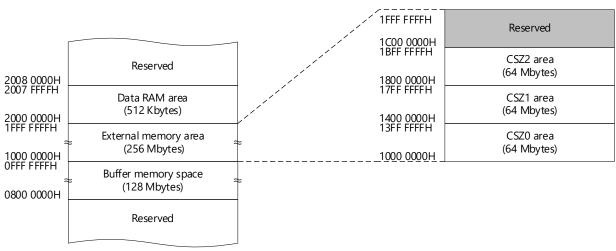

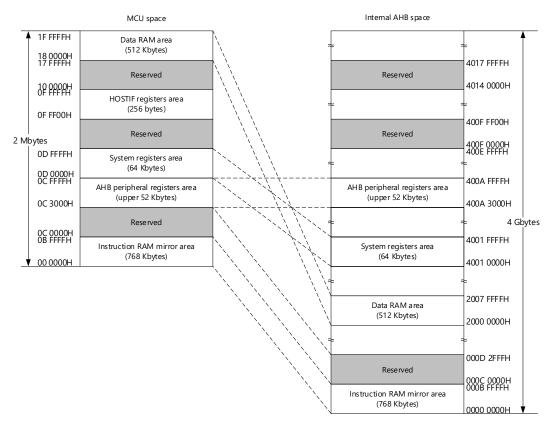

| 4.5 Base Addresses                                                                            | 54 |

| 4.6 Memory Maps                                                                               | 54 |

| 4.7 Exception Handling ······                                                                 |    |

| 4.7.1 List of interrupts ·····                                                                |    |

| 4.8 Peripheral Modules ······                                                                 |    |

| 4.9 I/O Standby Function                                                                      |    |

|                                                                                               |    |

| 5 PIN FUNCTIONS                                                                               | 63 |

| 5.1 Pin List ·····                                                                            |    |

| 5.2 Pin List by Function                                                                      |    |

| 5.2.1 Port pins and real-time port pins                                                       |    |

| 5.2.2 Ethernet pins                                                                           |    |

| 5.2.3 External SRAM interface pins                                                            |    |

| 5.2.4 External MCU interface pins                                                             |    |

| 5.2.5 Serial flash ROM interface pins                                                         |    |

| 5.2.6 DMA interface pins                                                                      |    |

| 5.2.7 External interrupt input pins                                                           | 76 |

| 5.2.8 Timer I/O pins                                                                          | 76 |

| 5.2.9 Watchdog timer output pin                                                               | 77 |

| 5.2.10 Serial interface pins                                                                  | 78 |

| 5.2.11 CC-Link IE Field pins                                                                  | 79 |

| 5.2.12 System pins                                                                            | 80 |

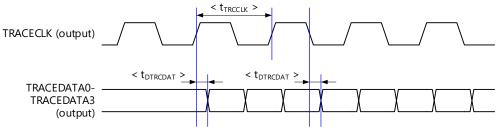

| 5.2.13 Trace pins                                                                             | 82 |

| 5.2.14 CPU power control pin                                                                  |    |

| 5.2.15 Test pins                                                                              |    |

| 5.2.16 Operating mode setting pins                                                            |    |

| 5.3 Pin States                                                                                |    |

| 5.3.1 Pin states when booting is from external memory                                         |    |

| 5.3.2 Pin states when booting is from external serial flash ROM                               |    |

| 5.3.3 Pin states when booting is for external MCU                                             |    |

| 5.4 Operating Mode Monitoring                                                                 |    |

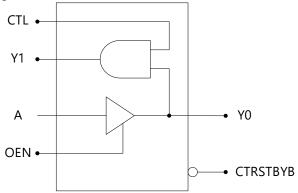

| 5.5 Buffer Switching······                                                                    |    |

| 5.6 Buffer Type of Pins and Handling of Unused Pins ·······                                   |    |

| 5.6.1 Port pins, real-time port pin buffer types, and handling of unused pins                 |    |

| 5.6.2 Buffer types of Ethernet pins and handling of unused pins                               |    |

|                                                                                               |    |

| 5.6.3 Buffer types of external SRAM / external MCU interface pins and handling of unused pins |    |

| 5.6.4 Buffer types of cC Link IE Field air and handling of unused pin                         |    |

| 5.6.5 Buffer types of CC-Link IE Field pin and handling of unused pin                         |    |

| 5.6.6 Buffer types of system pins and handling of unused pins                                 |    |

| 5.6.7 Buffer types of trace pins and handling of unused pins                                  |    |

| 5.6.8 Buffer types of test pins and handling of unused pins                                   | 99 |

| 5.6.9 Buffer types of operating mode setting pins and handling of unused pins | 99  |

|-------------------------------------------------------------------------------|-----|

| 5.6.10 Buffer types of reserved pins and pin handling                         | 100 |

| 6 ELECTRICAL CHARACTERISTICS                                                  | 101 |

| 6.1 Absolute Maximum Ratings                                                  | 102 |

| 6.2 Recommended Operating Conditions                                          | 102 |

| 6.3 DC Characteristics                                                        | 103 |

| 6.4 Pull-Up/Pull-Down Resistor Values ·····                                   | 103 |

| 6.5 Pin Capacitance ·····                                                     |     |

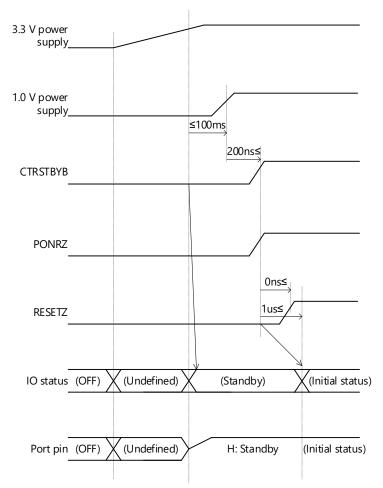

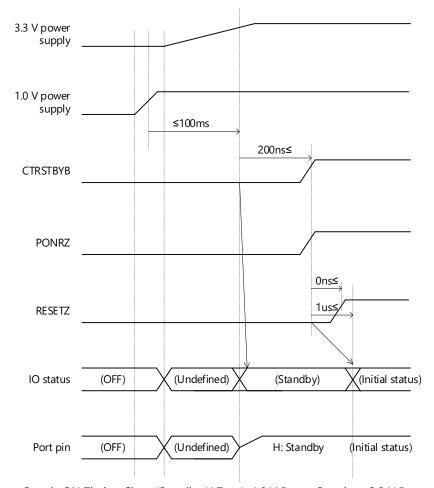

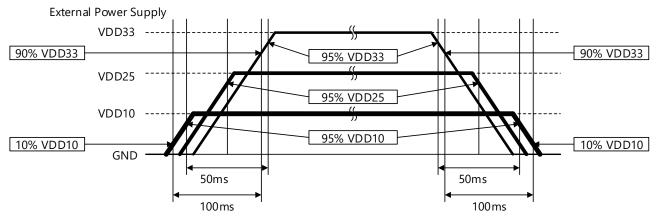

| 6.6 Power-On/Off Sequence ·····                                               |     |

| 6.7 AC Characteristics                                                        |     |

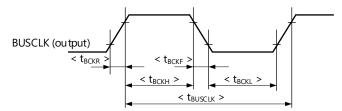

| 6.7.1 Clock pins ·····                                                        |     |

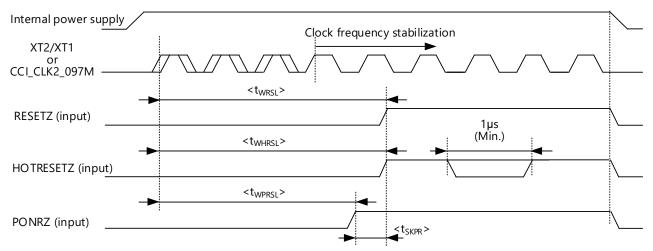

| 6.7.2 Reset pins ·····                                                        |     |

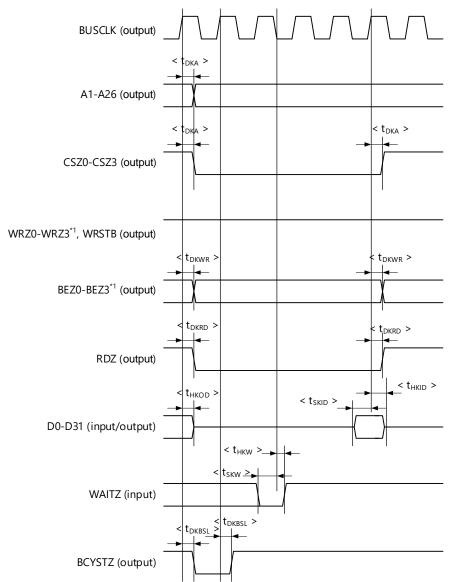

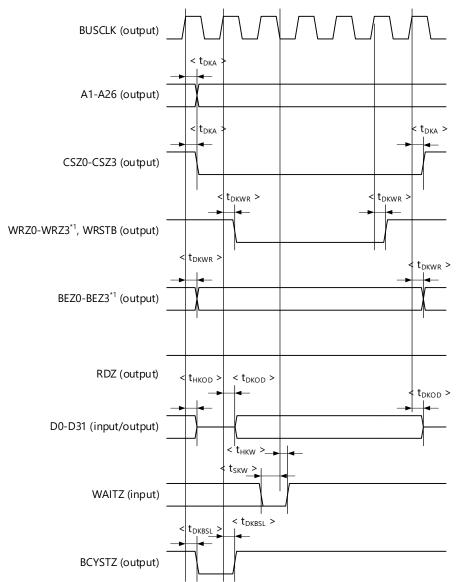

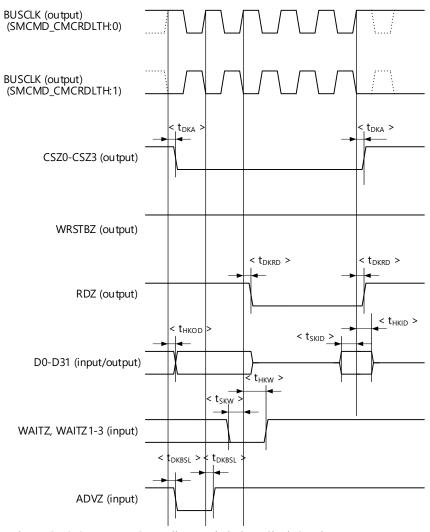

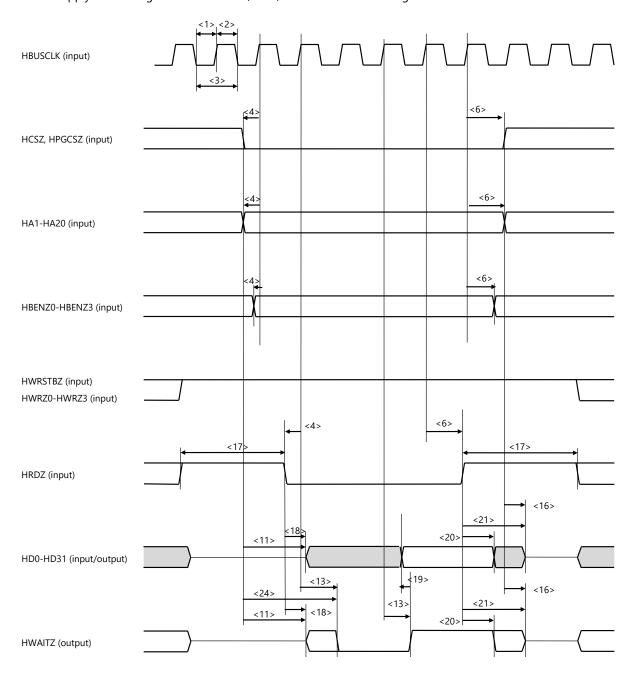

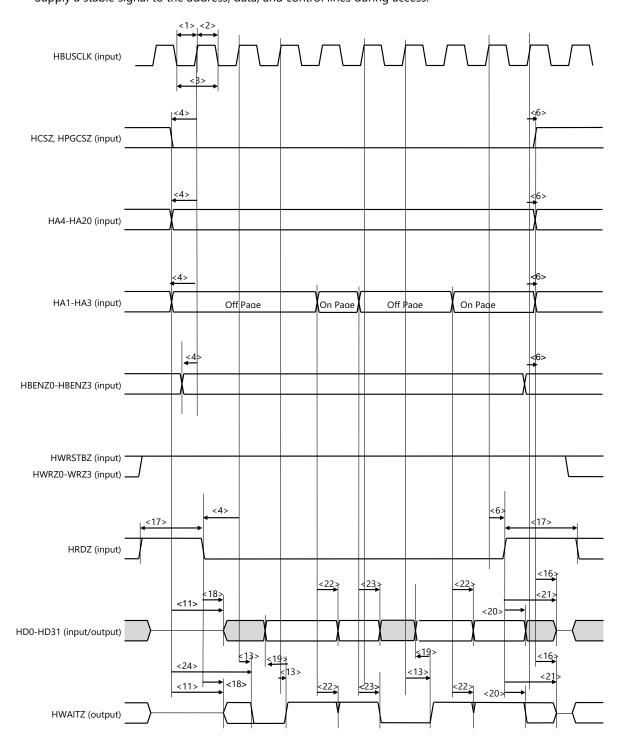

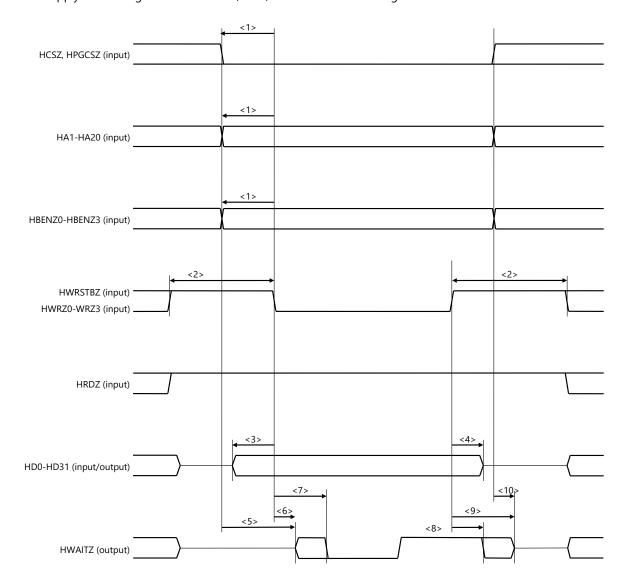

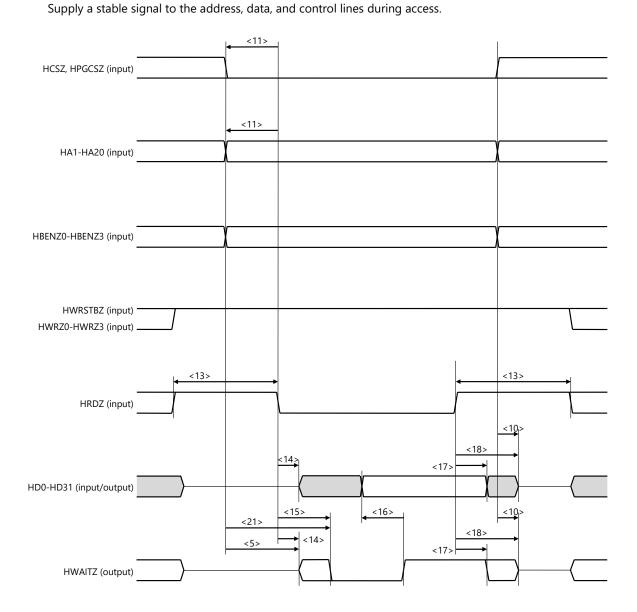

| 6.7.3 External memory interface pins ······                                   |     |

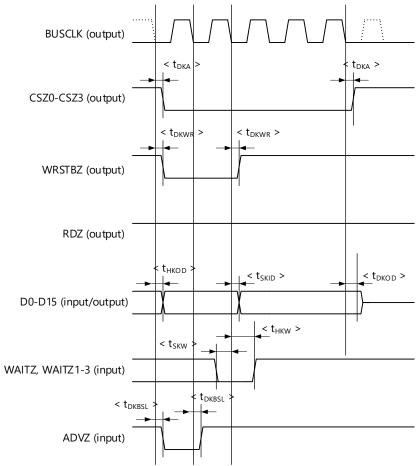

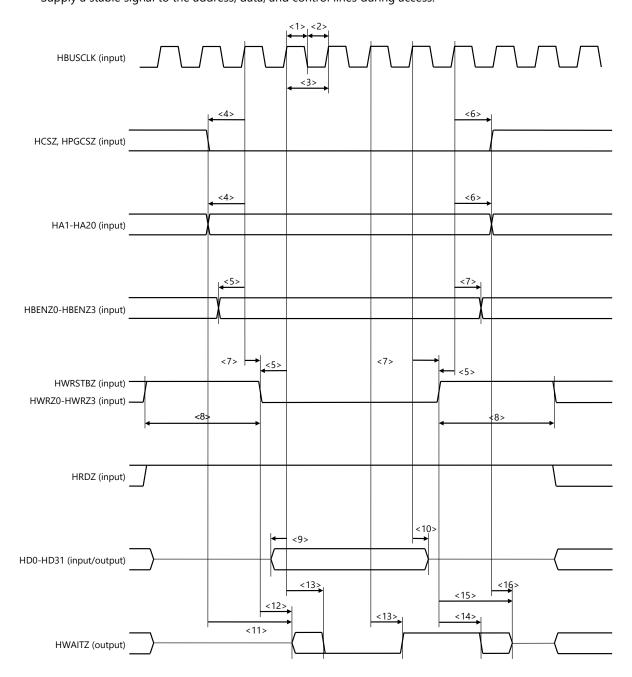

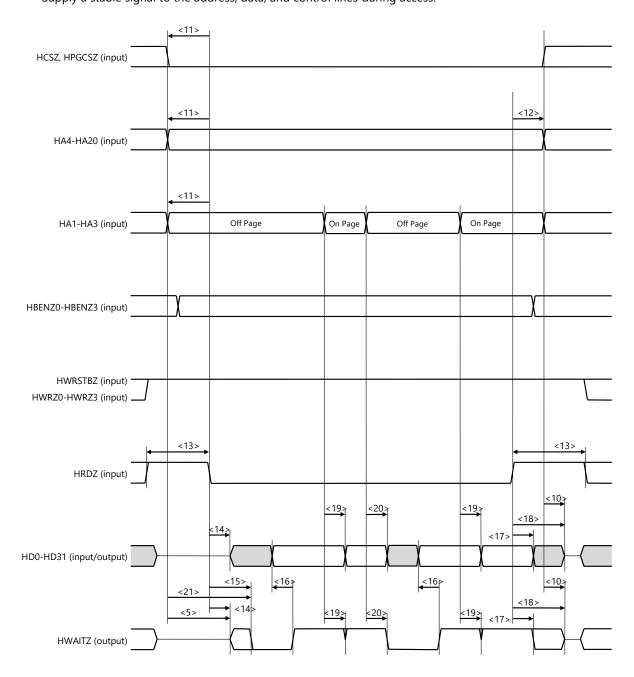

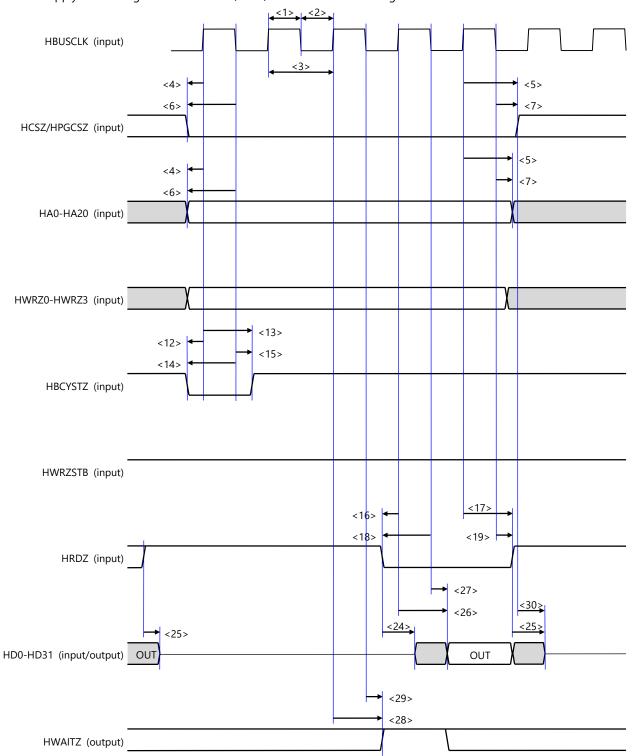

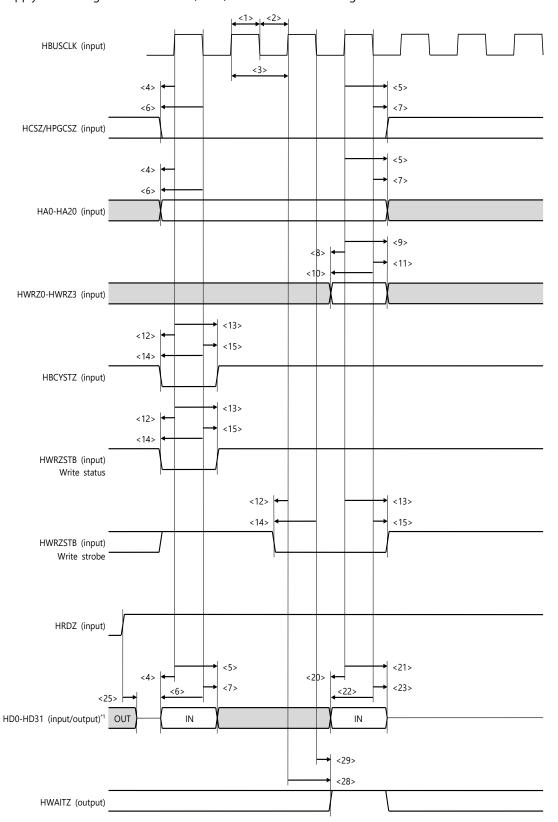

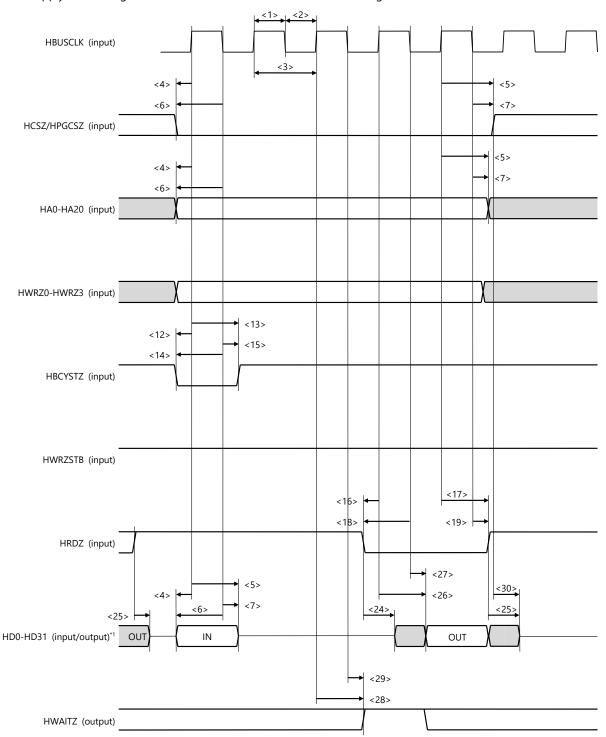

| 6.7.4 External MCU interface pins                                             |     |

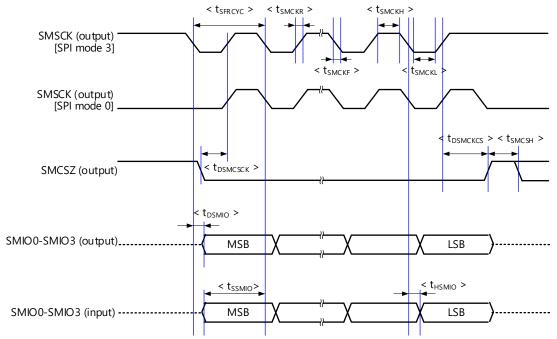

| 6.7.5 Serial flash ROM interface                                              |     |

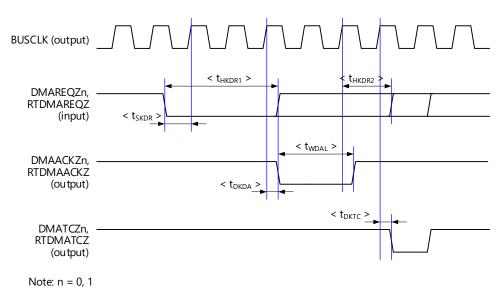

| 6.7.6 External DMA interface                                                  |     |

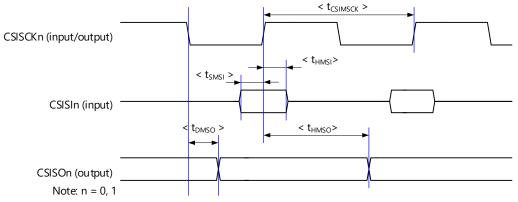

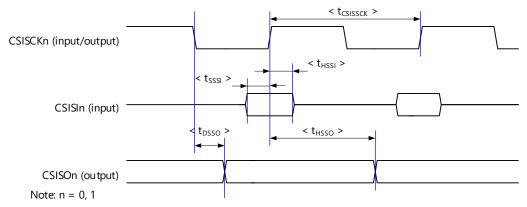

| 6.7.7 Clocked serial interface                                                |     |

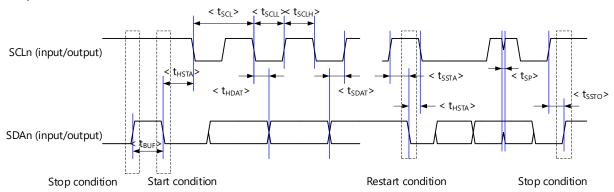

| 6.7.8 I2C interface                                                           |     |

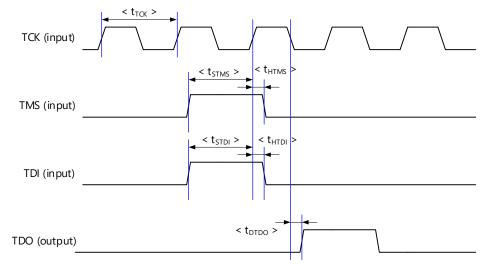

| 6.7.9 Debugging interface                                                     | 131 |

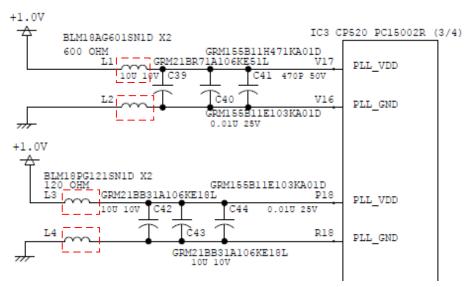

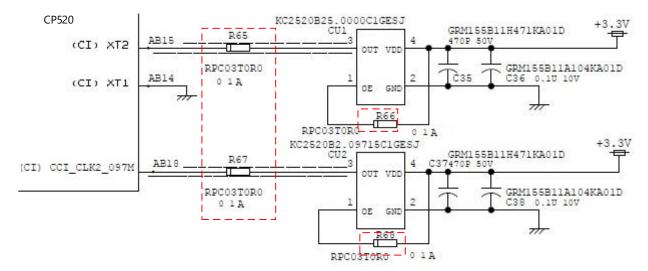

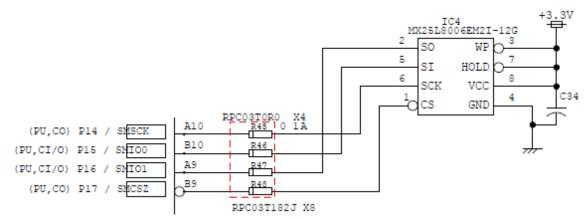

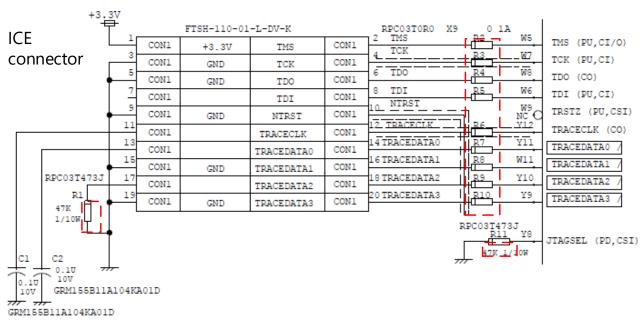

| 7 DEVELOPING A CP520 APPLICATION CIRCUIT                                      | 132 |

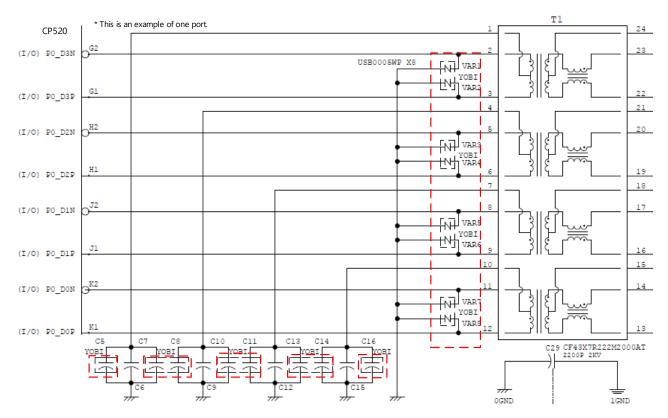

| 7.1 CP520 Application Circuit Diagram Example                                 | 132 |

| 7.2 Component List ······                                                     | 133 |

| 7.2.1 Component list (CP520 peripheral circuits)                              |     |

| 7.2.2 Component list (CP520 power supply peripheral circuit) ······           | 135 |

| 7.3 Board Design Precautions                                                  |     |

| 7.3.1 Component selection precautions ······                                  |     |

| 7.3.2 Circuit design precautions                                              |     |

| 7.3.3 Pattern design precautions ······                                       |     |

| 7.4 Noise Suppression Components                                              |     |

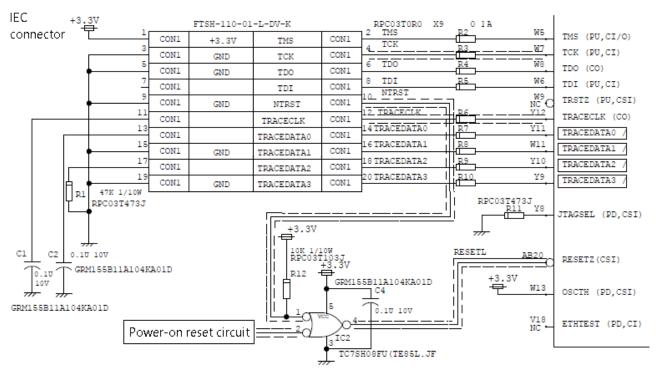

| 7.5 Circuits Required During Debugging                                        |     |

| 7.6 Thermal Characteristics                                                   |     |

| 7.7 LSI Handling Precautions                                                  |     |

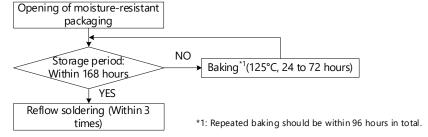

| 7.7.1 Opening precautions                                                     |     |

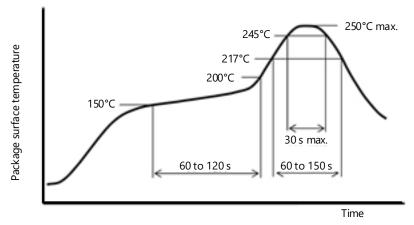

| 7.7.2 Recommended soldering conditions                                        | 145 |

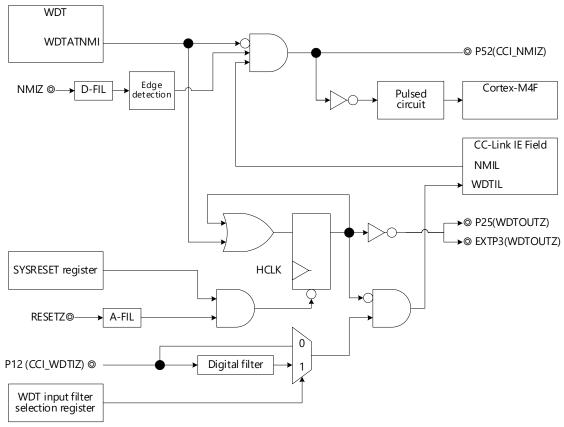

| 8 RESET                                                                       | 146 |

| 8.1 Reset Control Registers                                                   | 147 |

| 9 REGISTERS                                                                   | 148 |

| 9.1 Register List                                                             |     |

| 9.2 CC-Link IE Field Bus Bridge Control Registers                             |     |

| 9.2.1 CC-Link IE Field bus size control register (CIEBSC) ······              |     |

| 9.2.2 CC-Link IE Field bus bridge control register (CIESMC)                   | 149 |

| 9.2.3 CC-Link IE Field clock gate register (CIECLKGTD)······                  | 149 |

| 9.3 Clock Control Register 1 (CLKGTD1)······                                  |     |

| 9.4 DMA Trigger Factor Registers (DTFRn, RTDTFR)                              |     |

| 9.5 Timer Trigger Source Registers (TMTFR0-3, TMDTFR0-7)                      |     |

| 9.6 External Interrupt Mode Register 0 (INTM0)                                |     |

| 9.7 Trigger-Synchronous Port Source Registers (RP0TFR-RP3TFR)                 |     |

| 9.8 Noise Filter Configuration Register (NFC0)                                |     |

| 9.9 Operating Mode Monitor Register (MDMNT)                                   | 159 |

| 160 |

|-----|

| 162 |

| 162 |

| 165 |

| 166 |

| 166 |

| 167 |

| 168 |

| 169 |

| 170 |

| 170 |

| 171 |

| 172 |

| 172 |

| 173 |

| 175 |

| 176 |

| 178 |

| 179 |

| 186 |

| 186 |

| 188 |

| 189 |

| 190 |

| 192 |

| 192 |

| 193 |

| 193 |

| 194 |

| 195 |

| 199 |

| 200 |

| 201 |

| 202 |

| 202 |

| 203 |

| 204 |

| 205 |

| 205 |

| 206 |

| 200 |

| 207 |

| 207 |

| 209 |

| 211 |

| 211 |

| 211 |

| 218 |

| 220 |

| 224 |

| 225 |

| 229 |

|     |

| 232 |

|     |

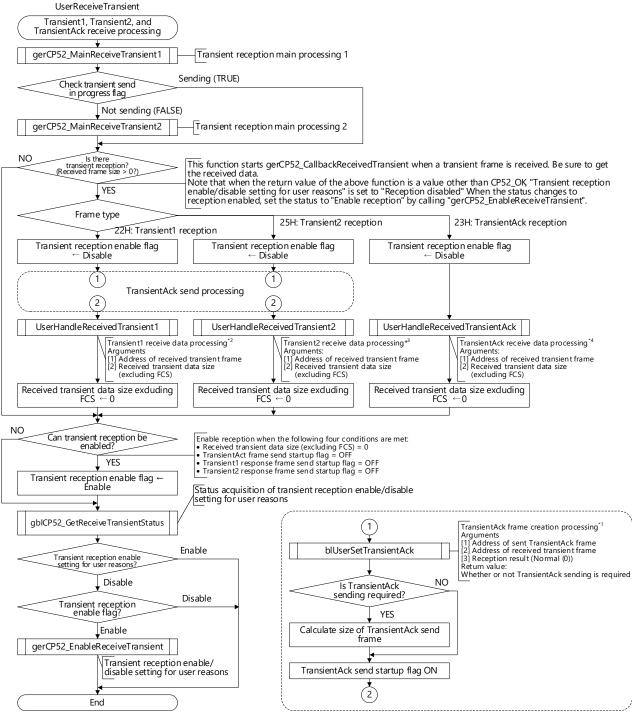

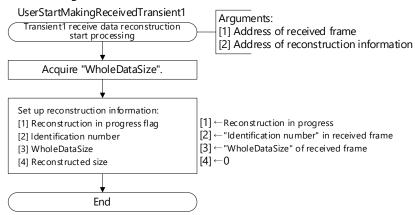

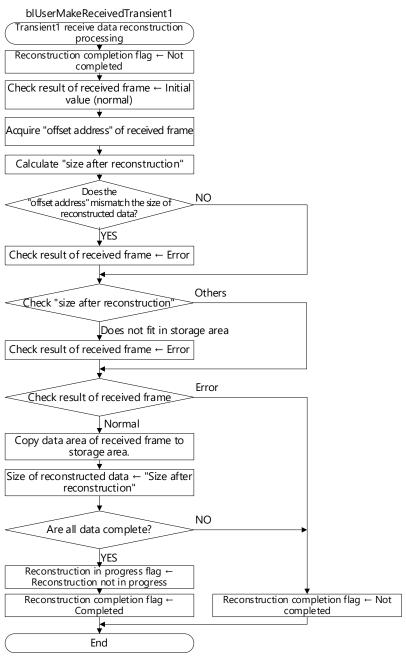

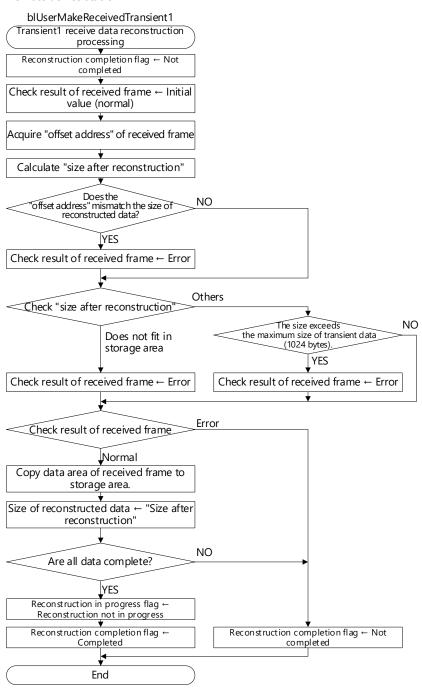

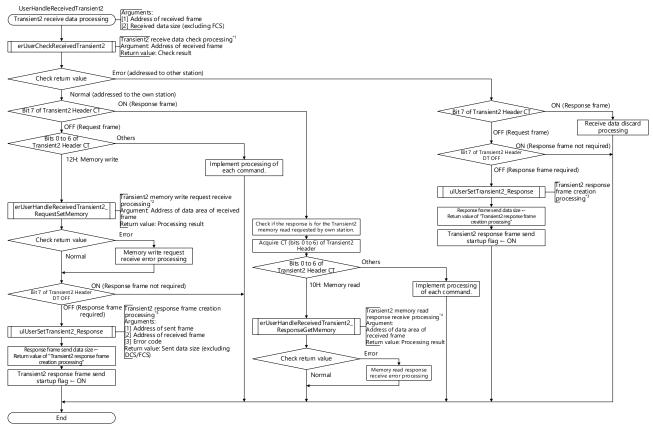

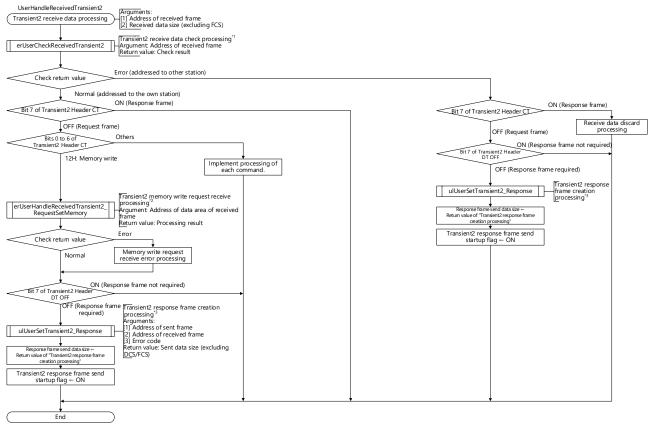

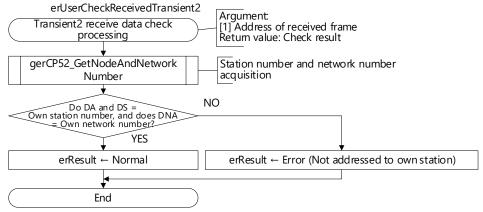

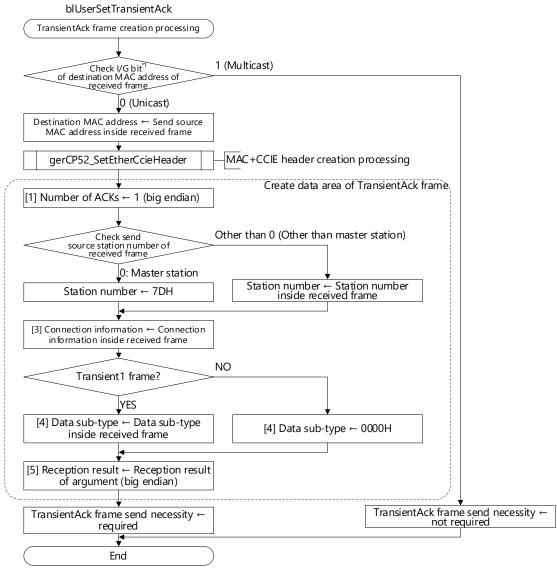

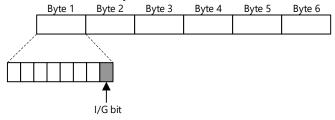

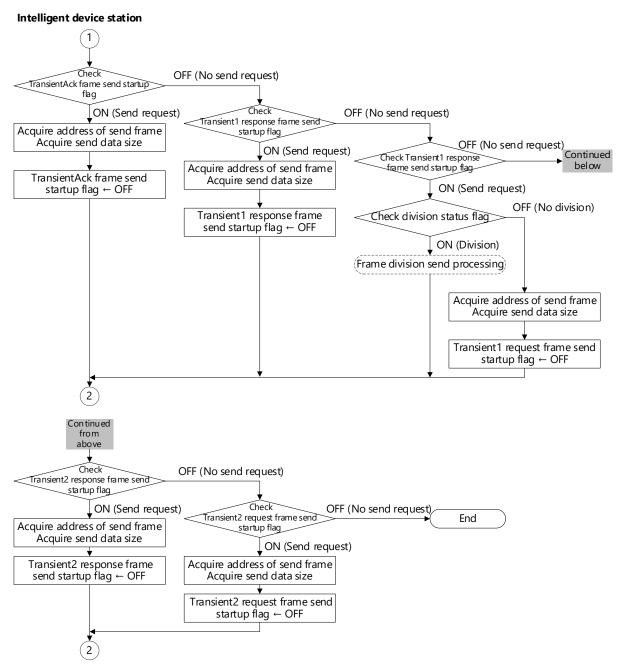

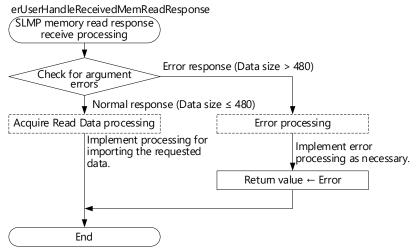

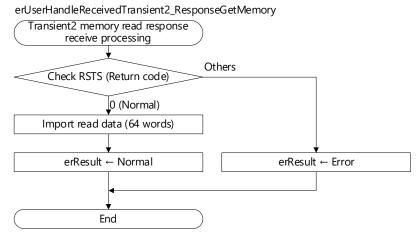

| 11.3.10 Transient reception ······                                              | 236 |

|---------------------------------------------------------------------------------|-----|

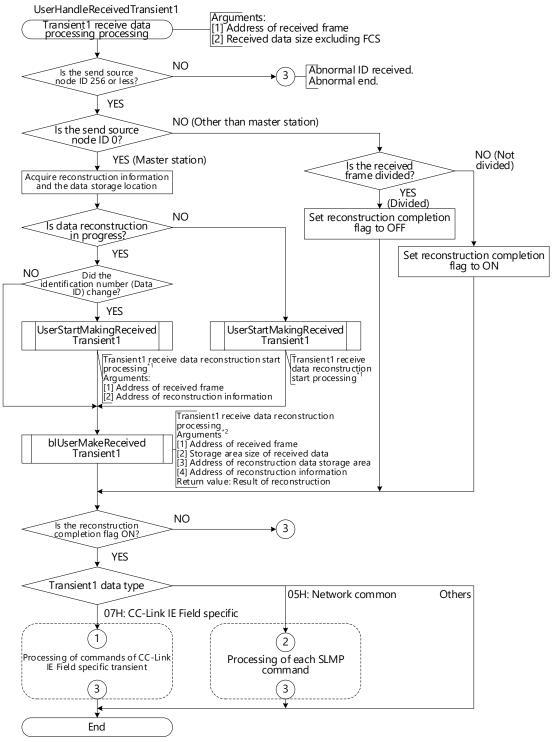

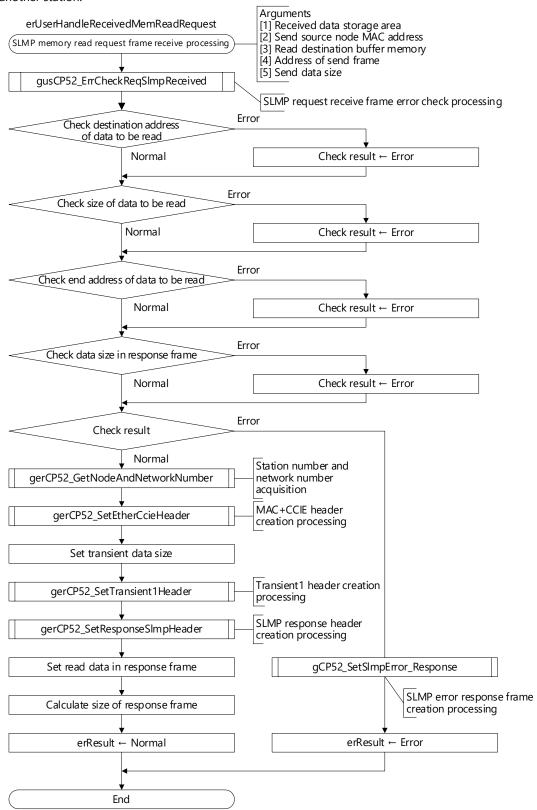

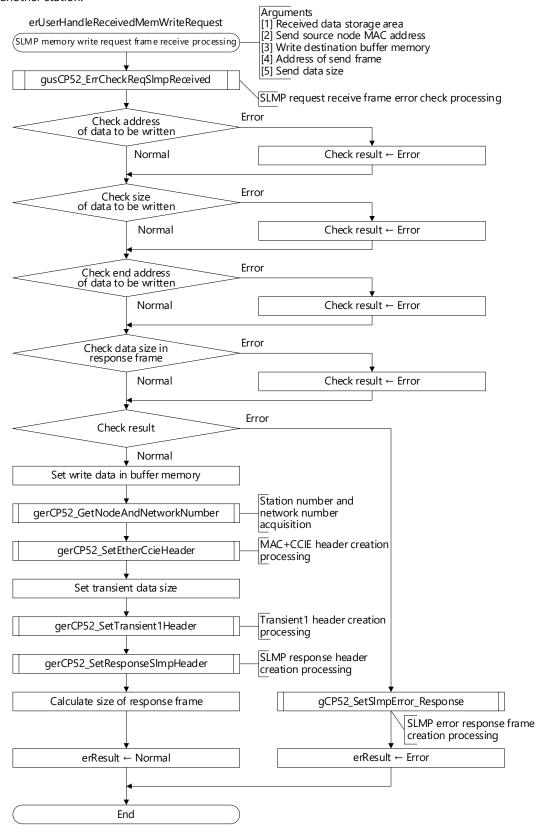

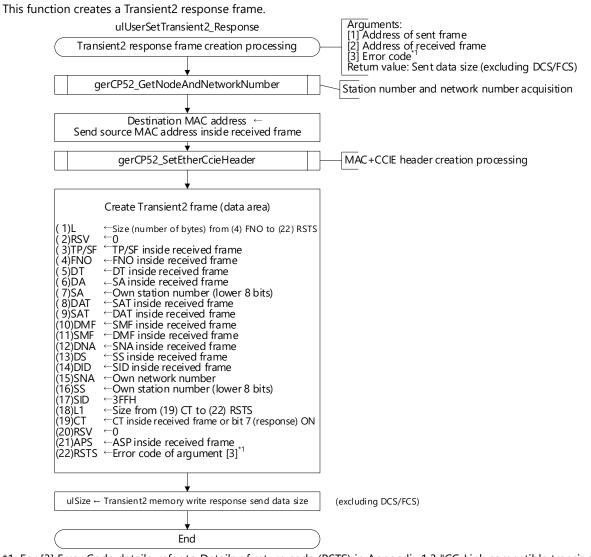

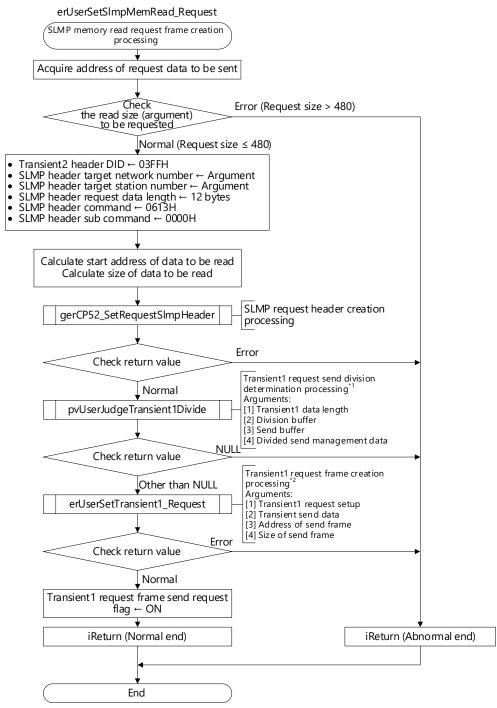

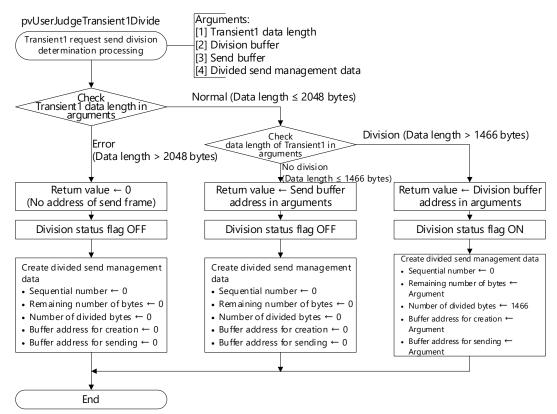

| 11.3.11 Transient request reception                                             | 238 |

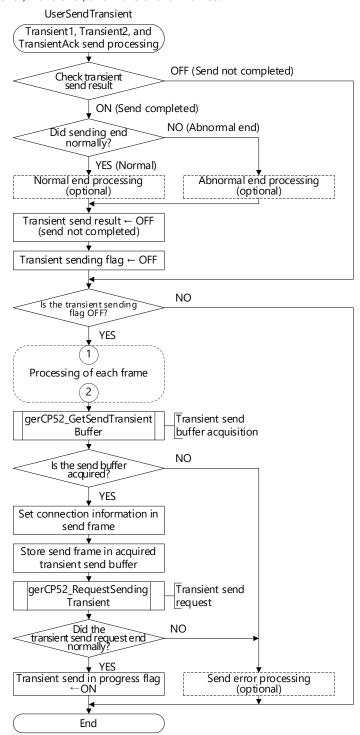

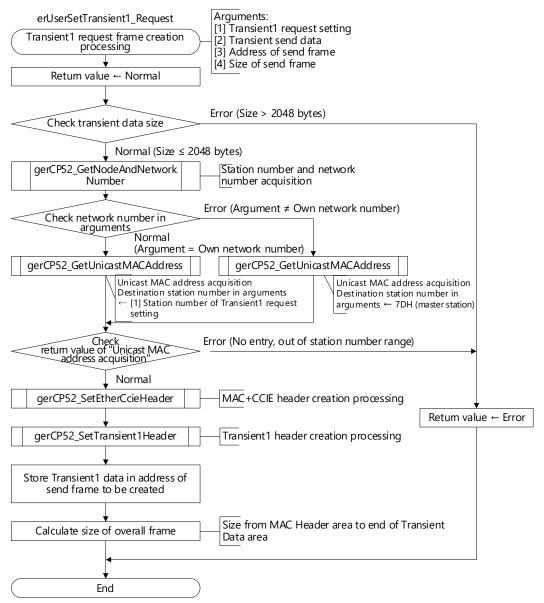

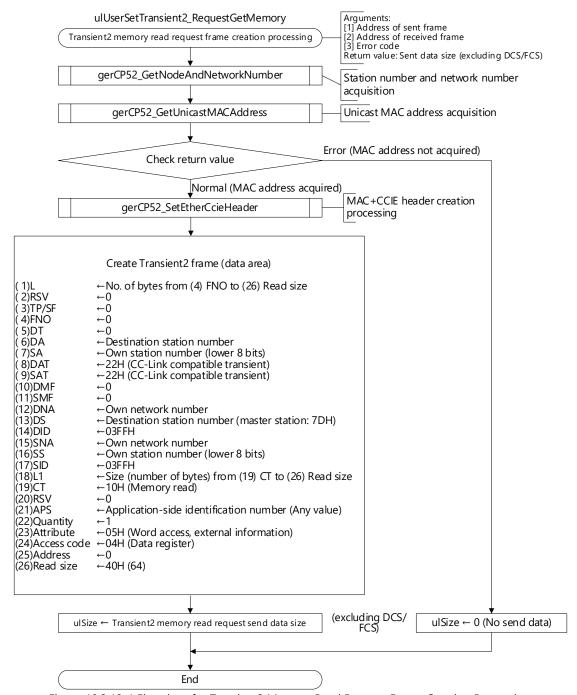

| 11.3.12 Transient send frame header creation                                    | 242 |

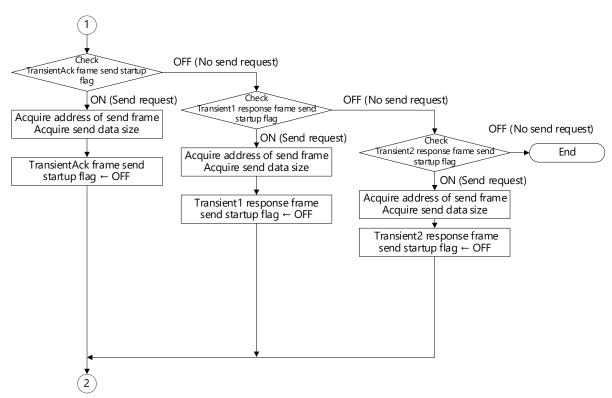

| 11.3.13 Transient send                                                          | 245 |

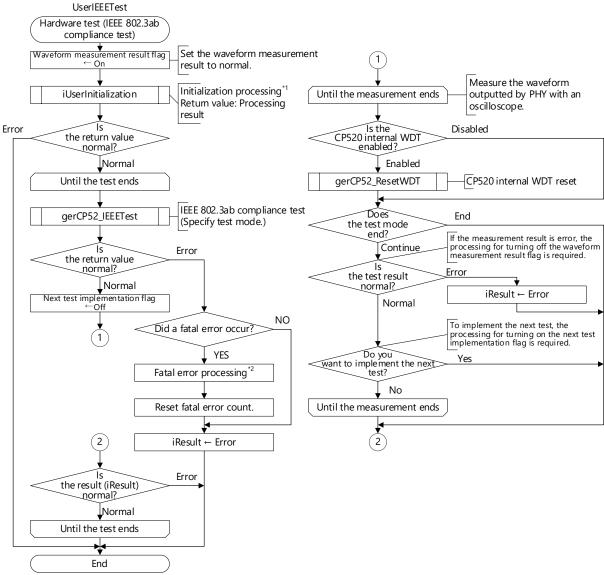

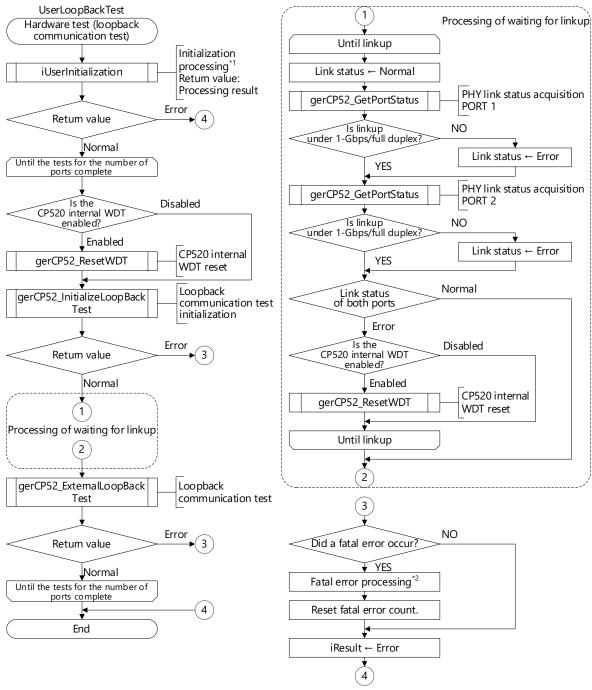

| 11.3.14 Hardware test ·····                                                     | 248 |

| 11.4 CP520 Driver Callback Function List                                        |     |

| 11.5 CP520 Driver Callback Function Details                                     | 250 |

| 12 LINK DEVICE SYSTEM AREA                                                      | 253 |

| 12.1 System Area Details                                                        | 254 |

| 13 TROUBLESHOOTING                                                              | 257 |

| 13.1 Hardware Design                                                            | 257 |

| 13.2 Software Design                                                            |     |

| 13.3 Protocol                                                                   |     |

| 13.4 Performance and Functions                                                  |     |

| 13.5 Conformance Test ·······                                                   |     |

| 13.6 Others                                                                     |     |

|                                                                                 |     |

| APPENDICES                                                                      | 263 |

| Appendix 1 Frame Format                                                         |     |

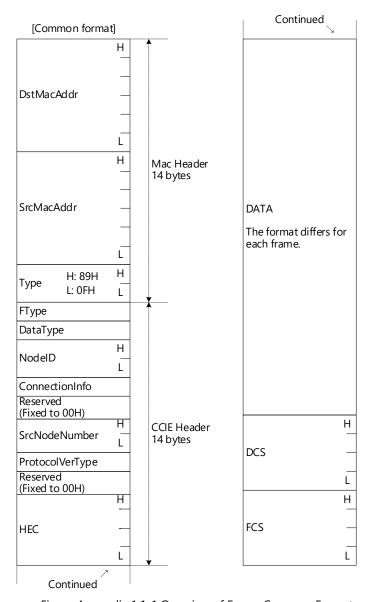

| Appendix 1.1 Common format                                                      |     |

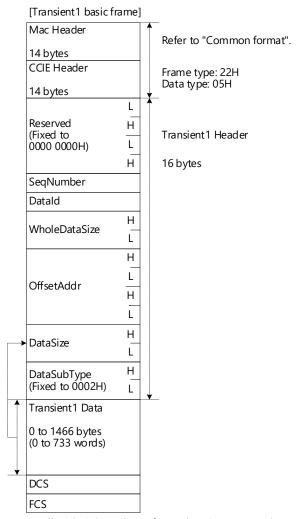

| Appendix 1.2 Transient1 frame ······                                            |     |

| Appendix 1.3 CC-Link compatible transient frame                                 |     |

| Appendix 1.3.1 Memory read                                                      |     |

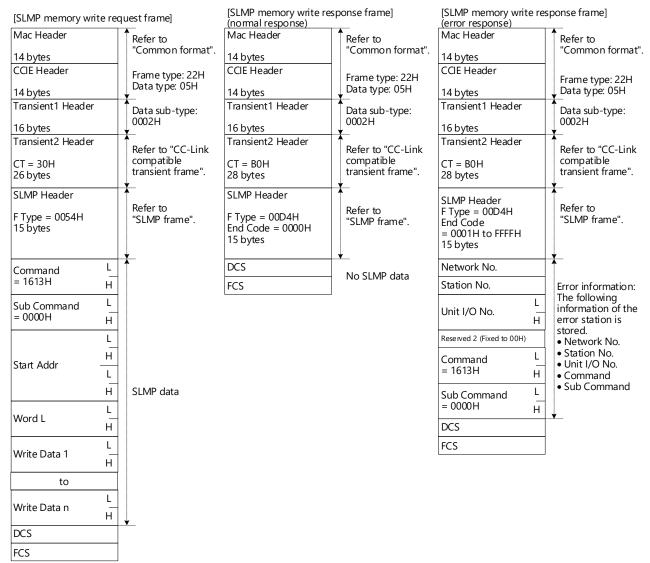

| Appendix 1.3.2 Memory write                                                     | 273 |

| Appendix 1.3.3 Access codes and attributes                                      |     |

| Appendix 1.4 SLMP frame                                                         | 276 |

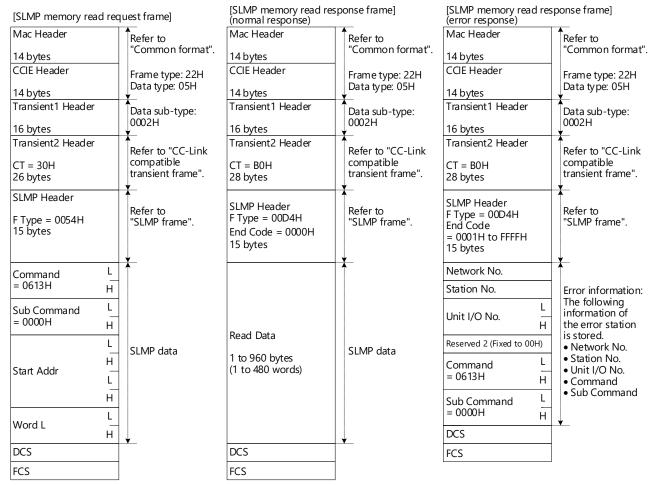

| Appendix 1.4.1 SLMP memory read frame                                           | 279 |

| Appendix 1.4.2 SLMP memory write frame                                          | 280 |

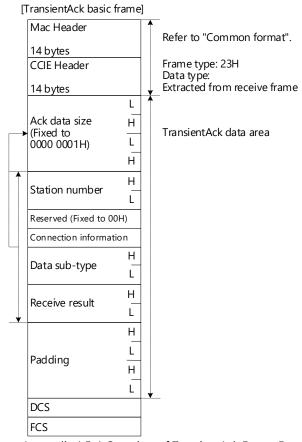

| Appendix 1.5 TransientAck frame ······                                          | 281 |

| Appendix 2 Port Functions                                                       | 282 |

| Appendix 2.1 Features                                                           |     |

| Appendix 2.2 Port configuration                                                 |     |

| Appendix 2.3 List of registers                                                  |     |

| Appendix 2.4 Register details                                                   |     |

| Appendix 2.4.1 Port registers (P, RP, EXTP)                                     | 288 |

| Appendix 2.4.2 Port mode registers (PM, RPM, EXTPM) ······                      | 289 |

| Appendix 2.4.3 Port mode control registers (PMC, RPMC, EXTPMC)                  | 290 |

| Appendix 2.4.4 Port function control registers (PFC, RPFC, EXTPFC)              |     |

| Appendix 2.4.5 Port function control expansion registers (PFCE, RPFCE, EXTPFCE) |     |

| Appendix 2.4.6 Port pin input registers (PIN, RPIN, EXTPIN) ······              |     |

| Appendix 2.5 List of selectable multiplexed functions                           |     |

| Appendix 2.6 Buffer switching registers (DRCTL)                                 |     |

| Appendix 2.6.1 Port 0 buffer switching register (DRCTLP0L, DRCTLP0H)            |     |

| Appendix 2.6.2 Port 1 buffer switching register (DRCTLP1L, DRCTLP1H)            |     |

| Appendix 2.6.3 Port 2 buffer switching register (DRCTLP2L, DRCTLP2H)            |     |

| Appendix 2.6.4 Port 3 buffer switching register (DRCTLP3L, DRCTLP3H)            |     |

| Appendix 2.6.5 Port 4 buffer switching register (DRCTLP4L, DRCTLP4H)            |     |

|                                                                                 |     |

| Appendix 2.6.6 Port 5 buffer switching register (DRCTLP5L, DRCTLP5H)            |     |

| Appendix 2.6.7 Port 6 buffer switching register (DRCTLP6L, DRCTLP6H)            |     |

| Appendix 2.6.8 Port 7 buffer switching register (DRCTLP7L, DRCTLP7H)            | 306 |

| Appendix 2.6.9 EXT port 0 buffer switching registers (DRCTLEXTP0L, DRCTLEXTP0H)   | 307 |

|-----------------------------------------------------------------------------------|-----|

| Appendix 2.6.10 EXT port 1 buffer switching register (DRCTLEXTP1L)                | 308 |

| Appendix 2.6.11 Real-time port 0 buffer switching register (DRCTLRP0L, DRCTLRP0H) | 309 |

| Appendix 2.6.12 Real-time port 1 buffer switching register (DRCTLRP1L, DRCTLRP1H) | 310 |

| Appendix 2.6.13 Real-time port 2 buffer switching register (DRCTLRP2L, DRCTLRP2H) | 311 |

| Appendix 2.6.14 Real-time port 3 buffer switching register (DRCTLRP3L, DRCTLRP3H) | 312 |

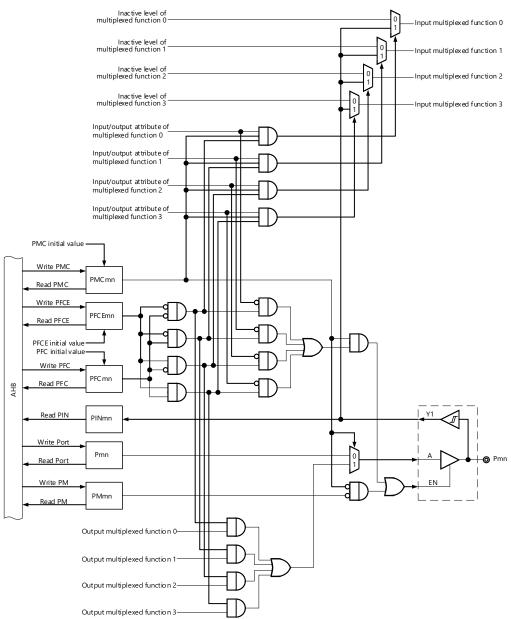

| Appendix 2.7 Operation of port functions                                          | 313 |

| Appendix 2.7.1 Reading and writing via I/O ports                                  | 313 |

| Appendix 2.7.2 Multiplexed function pin output state in control mode              | 313 |

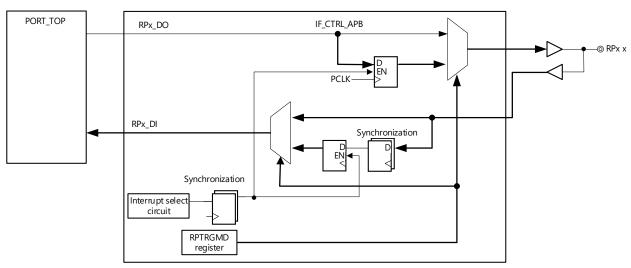

| Appendix 2.7.3 Trigger-synchronous ports (RP00-RP37)                              |     |

| Revisions                                                                         | 315 |

| Warranty ·····                                                                    | 317 |

| Trademarks                                                                        | 317 |

# Relevant Manuals

This manual does not describe the details on terms and functions of CC-Link IE Field Network. For the details, please refer to the following manuals.

| Related Manual Titles                                                                                                                                                                                                                                                                | Manual Number<br>(Model Name Code) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| [MELSEC iQ-R Ethernet/CC-Link IE User's Manual (Startup)] Specifications, procedures before operation, system configuration, wiring, and communication examples of Ethernet, CC-Link IE Controller Network, and CC-Link IE Field Network                                             | SH(NA)-081256ENG<br>(13JX09)       |

| [MELSEC iQ-R CC-Link IE Field Network User's Manual (Application)] Functions, parameter settings, programming, troubleshooting, I/O signals, and buffer memory of CC-Link IE Field Network                                                                                           | SH(NA)-081259ENG<br>(13JX18)       |

| [MELSEC-Q CC-Link IE Field Network Master/Local Module User's Manual] Specifications, procedures before operation, system configuration, settings, functions, programming, and troubleshooting of the CC-Link IE Field Network and MELSEC-Q series master/local module               | SH(NA)-080917ENG<br>(13JZ47)       |

| [MELSEC-L CC-Link IE Field Network Master/Local Module User's Manual] Specifications, procedures before operation, system configuration, installation, settings, functions, programming, and troubleshooting of the CC-Link IE Field Network and MELSEC-L series master/local module | SH(NA)-080972ENG<br>(13JZ54)       |

| [MELSEC-L CC-Link IE Field Network Head Module User's Manual] Specifications, procedures before operation, system configuration, installation, settings, and troubleshooting of the head module                                                                                      | SH(NA)-080919ENG<br>(13JZ48)       |

| [SLMP Reference Manual] Protocol (SLMP) used by external devices to read/write data from/to SLMP-compatible devices                                                                                                                                                                  | SH(NA)-080956ENG<br>(13JV23)       |

# Terms

| Unless otherwise specified, | , this manual uses the following terms.                                                                                                                                                                                                                                                                                            |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Term                        | Description                                                                                                                                                                                                                                                                                                                        |

| Another station             | A station other than own station                                                                                                                                                                                                                                                                                                   |

| Buffer memory               | Memory in a user application, where data (such as setting values and monitoring values) are stored                                                                                                                                                                                                                                 |

| CP520                       | A GbE-PHY built-in communication LSI for intelligent device stations and remote device stations of CC-Link IE Field Network                                                                                                                                                                                                        |

| CP520 application circuit   | A communication circuit of CC-Link IE Field Network. A circuit consists of CP520 and peripheral devices.                                                                                                                                                                                                                           |

| CP520 application product   | A CC-Link IE Field Network compatible product to be developed with reference to this manual                                                                                                                                                                                                                                        |

| CSP+                        | An abbreviation for Control & Communication System Profile. This is the specifications for describing information required for start-up, operation, and maintenance of CC-Link family compatible devices.                                                                                                                          |

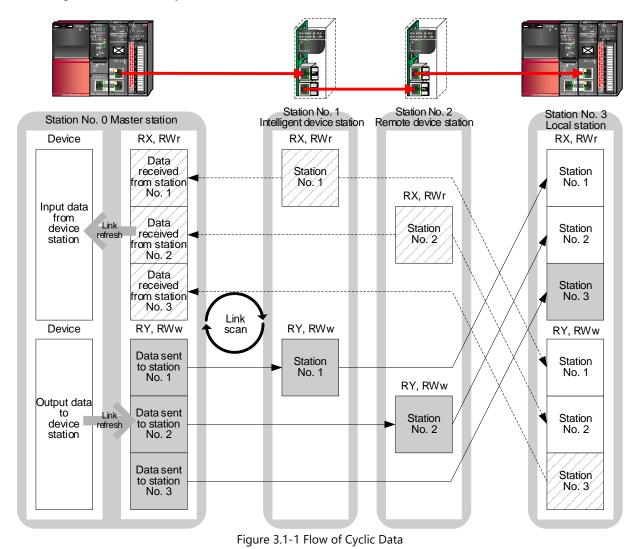

| Cyclic transmission         | A function by which data are periodically exchanged among stations on the same network using link devices                                                                                                                                                                                                                          |

| Data link                   | A generic term for cyclic transmission and transient transmission                                                                                                                                                                                                                                                                  |

| Device                      | Memory (X, Y, M, D, or others) in a programmable controller CPU, or memory in a user application, where data communicated with CP520 are stored                                                                                                                                                                                    |

| Device station              | A generic term for stations other than a master station: local station, intelligent device station, remote device station, remote I/O station                                                                                                                                                                                      |

| Disconnection               | A process of stopping data link if a data link error occurs                                                                                                                                                                                                                                                                        |

| End user                    | A purchaser and user of CC-Link family compatible products developed by users                                                                                                                                                                                                                                                      |

| GMII                        | An abbreviation for Gigabit Media-Independent Interface.<br>This is an interface for communicating data between the MAC port (MAC layer) and the PHY                                                                                                                                                                               |

| CV Mortes 2 /CV Mortes 2    | (physical layer) of CP520.                                                                                                                                                                                                                                                                                                         |

| GX Works2/GX Works3         | The product name of the software package for the MELSEC programmable controllers                                                                                                                                                                                                                                                   |

| GbE-PHY                     | An abbreviation for Gigabit Ethernet PHY. In this manual, the term refers to an IEEE 802.3 1000BASE-T compatible physical layer that has GMII.                                                                                                                                                                                     |

| Intelligent device station  | A station that exchanges I/O signals (bit data) and I/O data (word data) with the master station by cyclic transmission. This station can also perform transient transmission. This station responds to a transient transmission request from another station and also issues a transient transmission request to another station. |

| Link device                 | A device in a network module (RX, RY, RWr, and RWw)                                                                                                                                                                                                                                                                                |

| EITIK GEVICE                | A station that performs cyclic transmission and transient transmission with the master station                                                                                                                                                                                                                                     |

| Local station               | and other local stations.  This station receives data in RX, RY, RWr, and RWw of other device stations in cyclic transmission.                                                                                                                                                                                                     |

| MDC                         | An abbreviation for Management Data Clock. This is an MDIO clock specified in GMII. This configures a management interface together with MDIO.                                                                                                                                                                                     |

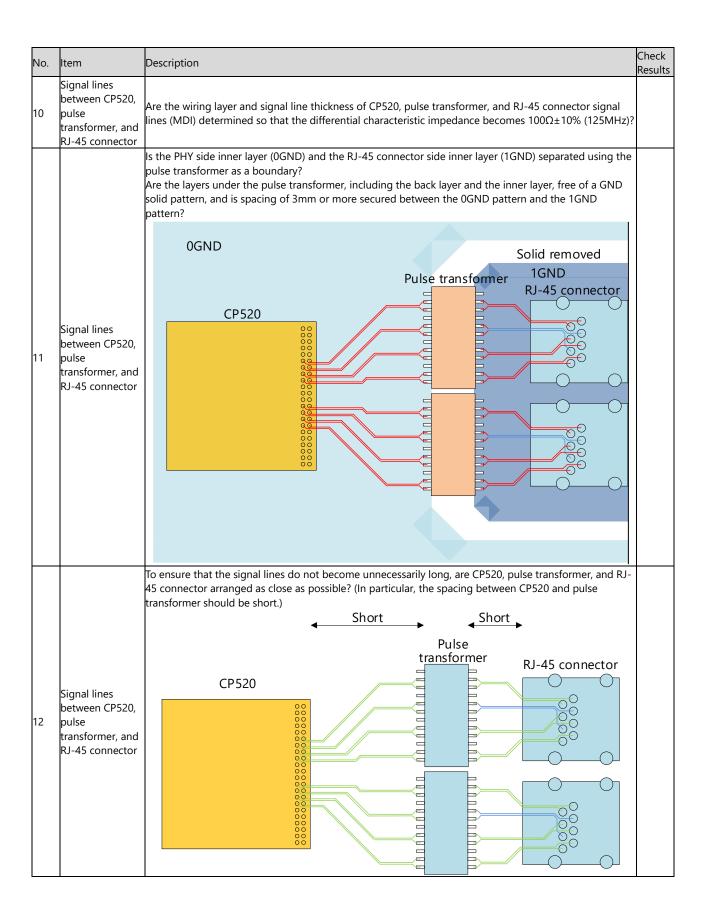

| MDI                         | An abbreviation for Medium Dependent Interface. This is an interface for communicating data between CP520 and a pulse transformer and between a pulse transformer and an RJ-45 connecter.                                                                                                                                          |

| MDIO                        | An abbreviation for Management Data Input/Output. This is a data input/output bus for accessing PHY registers specified in GMII. This configures a management interface together with MDC.                                                                                                                                         |

| МІВ                         | An abbreviation for Management Information Base. This is a management information base for saving the communication status of CP520.                                                                                                                                                                                               |

| Management interface        | An interface for accessing PHY registers from CP520. The interface consists of MDIO and MDC.                                                                                                                                                                                                                                       |

| Master station              | A station that controls CC-Link IE Field Network. This station can perform cyclic transmission and transient transmission with all stations.                                                                                                                                                                                       |

| Master/local module         | An abbreviation for the RJ71GF11-T2, QJ71GF11-T2, or LJ71GF11-T2 CC-Link IE Field Network master/local module, and also a generic term for the RJ71EN71 and RnENCPU modules when the CC-Link IE Field Network function is used                                                                                                     |

| Own station                 | An intelligent device station or remote device station to be developed based on this manual                                                                                                                                                                                                                                        |

| PHY                         | An abbreviation for the physical layer. In this manual, the term refers to a portion of CP520 functions, that converts logic signals into actual electrical signals in an interface such as Ethernet.                                                                                                                              |

| R-IN32M4-CL2                | An industrial Ethernet communication LSI of Renesas Electronics Corporation                                                                                                                                                                                                                                                        |

| Remote device station       | A station that exchanges I/O signals (bit data) and I/O data (word data) with the master station by cyclic transmission.                                                                                                                                                                                                           |

|                             | This station responds to a transient transmission request from another station.                                                                                                                                                                                                                                                    |

| Term                   | Description                                                                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Remote input (RX)      | Bit data input from a device station to the master station                                                                                                                                              |

| Remote output (RY)     | Bit data output from the master station to a device station                                                                                                                                             |

| Remote register (RWr)  | Word data input from a device station to the master station                                                                                                                                             |

| Remote register (RWw)  | Word data output from the master station to a device station                                                                                                                                            |

| Return                 | A process of restarting data link when a station recovers from an error                                                                                                                                 |

| SLMP                   | An abbreviation for Seamless Message Protocol. This is a protocol used to access an SLMP-compatible device or a programmable controller connected to an SLMP-compatible device from an external device. |

| ISTATION               | An element that forms a network and sends/receives/transfers data. The term, node, is used with the same meaning.                                                                                       |

| Station number         | A unique number assigned to stations in a network                                                                                                                                                       |

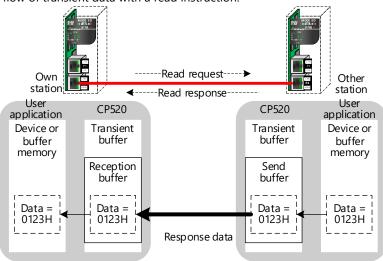

| Transient transmission | A function that communicates data with another station when requested by a user application                                                                                                             |

| II ICAr                | A manufacturer who develops and sells CC-Link family compatible products based on this manual. The terms, vendor and partner manufacturer, are used with the same meaning.                              |

# **Usage Precautions**

- (1) The intellectual property rights of the information provided on the CD-ROM included with this manual belong to Mitsubishi Electric. Reprinting the information without the consent of Mitsubishi Electric and reproduction of the information for any purpose other than the development of an intelligent device station or a remote device station is prohibited. Distribution of a product (object code or the like) after sample code compilation, however, is unrestricted.

- (2) Before using the software provided on the CD-ROM included with this manual, check the "END-USER SOFTWARE LICENSE AGREEMENT" (CP520\_Software\_License\_Agreement\_e.pdf) provided on the same CD-ROM.

- (3) The sample code described in this manual is for the development of an intelligent device station or a remote device station using CP520. The sample code indicates an example of use of the materials herein; its operation is not guaranteed by Mitsubishi Electric.

# **Address Notation**

This manual uses byte addresses, unless otherwise specified.

# **Radix Notation**

| This manual uses the following radix notation, unless otherwise specified. |                                                                |         |

|----------------------------------------------------------------------------|----------------------------------------------------------------|---------|

| Radix                                                                      | Description                                                    | Example |

| Binary                                                                     | "b" is added at the end of the number to indicate bit.         | "0b"    |

| Decimal                                                                    | Nothing is added at the end of the number.                     | "0"     |

| Hexadecimal                                                                | "H" is added at the end of the number to indicate hexadecimal. | "10BAH" |

# **CC-Link Partner Association**

#### (1) Specifications

The materials related to this manual include the specifications published by the CC-Link Partner Association below. For CC-Link IE Field Network and SLMP details, download and refer to these specifications from the CC-Link Partner Association website.

| Document Title                                                              | Document No.     |

|-----------------------------------------------------------------------------|------------------|

| CC-Link IE Field Network Specification (Overview)                           | BAP-C2005ENG-001 |

| CC-Link IE Field Network Specification (Physical Layer and Data Link Layer) | BAP-C2005ENG-002 |

| CC-Link IE Field Network Specification (Application Layer Service)          | BAP-C2005ENG-003 |

| CC-Link IE Field Network Specification (Application Layer Protocol)         | BAP-C2005ENG-004 |

| CC-Link IE Field Network Specification (Communication Profile)              | BAP-C2005ENG-005 |

| CC-Link IE Field Network Specification (Implementation Rules)               | BAP-C2005ENG-006 |

| CC-Link IE Field Network Specification (Device Profile)                     | BAP-C2005ENG-007 |

| SLMP (Seamless Message Protocol) Specification (Overview)                   | BAP-C2006ENG-001 |

| SLMP (Seamless Message Protocol) Specification (Services)                   | BAP-C2006ENG-002 |

| SLMP (Seamless Message Protocol) Specification (Protocol)                   | BAP-C2006ENG-003 |

| SLMP Reference Manual                                                       | BAP-C3002-001    |

#### (2) CC-Link IE Field Utility

This is a tool that simulates the master station on a personal computer. The user can simulate the master station on a personal computer without having the actual master station. Download the tool from the CC-Link Partner Association website as necessary.

| Document Title/Related Tool               | Document No. |

|-------------------------------------------|--------------|

| CC-Link IE Field Utility                  | -            |

| CC-Link IE Field Utility Operation manual | -            |

#### (3) Conformance test

When a product is developed based on the information in this manual, the product must undergo a conformance test implemented by the CC-Link Partner Association. For conformance test details, download and refer to the following document from the CC-Link Partner Association website.

| Document Title                                                                      | Document No.     |

|-------------------------------------------------------------------------------------|------------------|

| CC-Link IE Field Network Intelligent Device Station Conformance Test Specifications | BAP-C0401ENG-037 |

| CC-Link IE Field Network Remote Device Station Conformance Test Specification       | BAP-C0401ENG-041 |

#### (4) Creating a Control & Communication System Profile (CSP+)

The conformance test includes verification of CSP+. CSP+ files must be created in advance. For CSP+ details, download and refer to the following documents from the CC-Link Partner Association website.

From the same website, other relevant documents and tool that help users create CSP+ files can also be download.

| Document Title/Related Tool                                | Document No.     |

|------------------------------------------------------------|------------------|

| Control & Communication System Profile Specification       | BAP-C2008ENG-001 |

| Control & Communication System Profile Creation Guidelines | -                |

| CSP+ profile creation support tool                         | _                |

| Sample CSP+ Files                                          | -                |

| CSP+ Templates                                             | _                |

## (5) 1000BASE-T compliance test

The conformance test includes verification by a 1000BASE-T compliance test (a waveform test based on IEEE 802.3 specifications), which requires implementation by the user.

There are testing laboratories capable of implementing the 1000BASE-T compliance test. For details, contact the CC-Link Partner Association.

# (6) Inquiries

To request materials published by the CC-Link Partner Association and for conformance test details, please contact the following:

TEL: +81-52-919-1588 FAX: +81-52-916-8655 E-mail: <u>info@cc-link.org</u> Web: <u>http://www.cc-link.org/</u>

## 1 OVERVIEW

This manual describes how to develop an intelligent device station or remote device station for CC-Link IE Field Network using "CC-Link IE Field Network intelligent device stations and remote device stations communication LSI CP520 with GbE-PHY".

The main information included in this manual is as follows:

- · CP520 specifications

- · CP520 application circuit design

- · User program design

- · CP520 driver specifications

## 1.1 Development Features

CP520 is an LSI that integrates the communication IP core for CC-Link IE Field Network, CPU, and GbE-PHY. This integrated LSI allows you to reduce CPU and GbE-PHY related development costs and manhours. CP520-based development offers the following features:

- (1) CP520-based development allows you to develop an intelligent device station or remote device station for CC-Link IE Field Network without awareness of protocol.

- (2) GbE-PHY in CP520 facilitates the designing of communication circuit patterns. In addition, only a small number of peripheral components and circuits are required for CPU and GbE-PHY, allowing the development of more compact circuit boards.

- (3) A sample code is provided that can be easily customized in accordance with user hardware specifications and applications.

- (4) CP520 includes HW-RTOS, reducing the CPU load and achieving low power consumption in the developed device.

#### 1.2 Specifications of CP520 Hardware

The following table lists the specifications of CP520 hardware.

Table 1.2-1 Hardware Specifications

| Item              |                | Description                                              |  |

|-------------------|----------------|----------------------------------------------------------|--|

| Outer             | Number of pins | BGA 484 pins                                             |  |

| appearance        | Size           | 23mm × 23mm                                              |  |

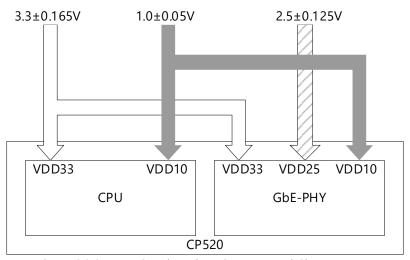

| Power supply v    | oltage         | 3.3V±5%, 2.5V±5%, 1.0V±5%                                |  |

| Operating ambient |                | -40 to 85°C                                              |  |

| temperature       |                |                                                          |  |

| CPU               |                | Integrated Arm® Cortex®-M4F processor with FPU (100 MHz) |  |

| Instruction RAM   |                | 768 Kbytes, built in (ECC compatible)                    |  |

| Data RAM          |                | 512 Kbytes (ECC compatible)                              |  |

| Buffer RAM        |                | 64 Kbytes (ECC compatible)                               |  |

| I/O ports         |                | CMOS I/Os: 106 maximum                                   |  |

| Ethernet PHY      |                | 1000BASE-T GbE-PHY (built-in) × 2 ports                  |  |

# 1.3 Communication Specifications of CP520 Application Products

The following table lists the CP520 communication specifications related to CC-Link IE Field Network.

Table 1.3-1 Communication Specifications of CC-Link IE Field Network

| ltem                               |          | Description                                                                                                                                                                                                                                       |                                       |  |

|------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|

| Station type                       |          | Intelligent device station or remote device station                                                                                                                                                                                               |                                       |  |

| Station number                     |          | 1 to 120                                                                                                                                                                                                                                          |                                       |  |

| Network number                     |          | 1 to 239                                                                                                                                                                                                                                          |                                       |  |

| Communication spec                 | ed       | 1Gbps                                                                                                                                                                                                                                             |                                       |  |

| Network topology                   |          | Line, star, and ring (Coexistence of line topo                                                                                                                                                                                                    | ology and star topology is possible.) |  |

| Connection cable                   |          | Ethernet cable that satisfies 1000BASE-T standards                                                                                                                                                                                                |                                       |  |

| Maximum station-to distance        | -station | (Category 5e or higher, double shielded, STP, straight cable)  100m                                                                                                                                                                               |                                       |  |

| sta Overall cable distance Sta Rin |          | Line topology: 12000m (when cables are connected to 1 master station and 120 device stations)  Star topology: Depends on the system configuration.  Ring topology: 12100m (when cables are connected to 1 master station and 120 device stations) |                                       |  |

| Number of cascade connections      |          | Up to 20                                                                                                                                                                                                                                          |                                       |  |

| Cyclic transmission                |          | Intelligent device station                                                                                                                                                                                                                        | Remote device station                 |  |

| Maximum                            | RX       | 2048 points (2048 bits), 256 bytes                                                                                                                                                                                                                | 128 points (128 bits), 16 bytes       |  |

| number of link                     | RY       | 2048 points (2048 bits), 256 bytes                                                                                                                                                                                                                | 128 points (128 bits), 16 bytes       |  |

| points per                         | RWr      | 1024 points (1024 words), 2048 bytes                                                                                                                                                                                                              | 64 points (64 words), 128 bytes       |  |

| station                            | RWw      | 1024 points (1024 words), 2048 bytes                                                                                                                                                                                                              | 64 points (64 words), 128 bytes       |  |

| Transient transmissio              | n        | Intelligent device station                                                                                                                                                                                                                        | Remote device station                 |  |

| Client function                    |          | Supported                                                                                                                                                                                                                                         | Not supported                         |  |

| Server function                    |          | Supported                                                                                                                                                                                                                                         | Supported                             |  |

| Data size*1                        |          | 2048 bytes                                                                                                                                                                                                                                        | 1024 bytes                            |  |

| Dedicated instruction              |          | RIRD/RIWT can be received by customizing the sample code.                                                                                                                                                                                         |                                       |  |

| Oth <u>er functions</u>            |          | -                                                                                                                                                                                                                                                 |                                       |  |

| Diagnostic function                |          | CC-Link IE Field Network diagnostic function                                                                                                                                                                                                      |                                       |  |

| Temporary error station            | invalid  | Supported                                                                                                                                                                                                                                         |                                       |  |

| Fast linkup                        |          | Supported                                                                                                                                                                                                                                         |                                       |  |

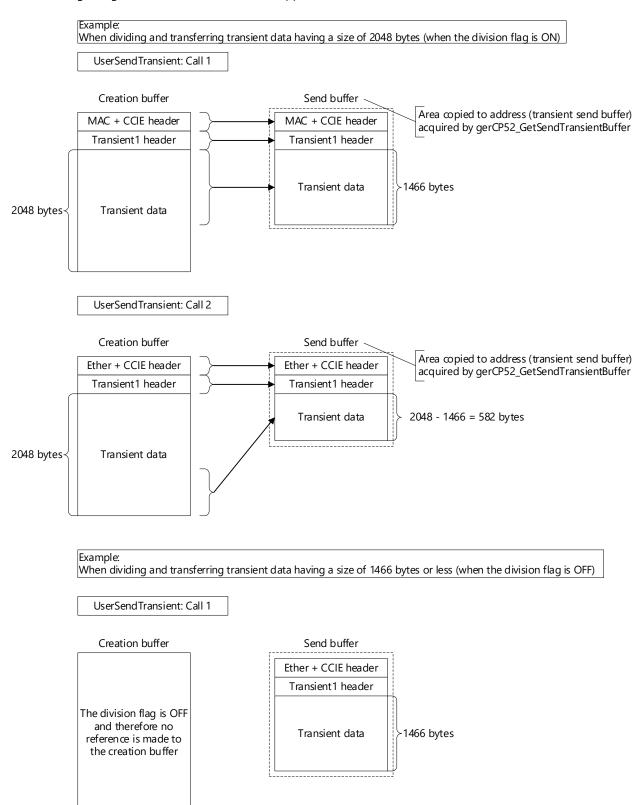

<sup>\*1:</sup> When the transient frame to be sent or received exceeds 1518 bytes, the transient frame is divided and sent or received in blocks.

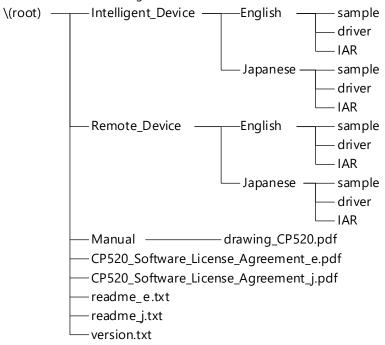

The following describes the folder configuration and files included in the CD-ROM provided with this manual. The folder configuration and files of data downloaded from the Mitsubishi Electric FA site are the same as those of the CD-ROM.

(1) Folder configuration of CD-ROM

The following shows the CD-ROM folder configuration.

Figure 1.4-1 CD-ROM Folder Configuration Diagram

# (2) CD-ROM file overview

The following provides an overview of the files included in the CD-ROM.

Table 1.4-1 File Overview

| Folder Name            |                     | File Name                                  | Description                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------------------|---------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Intelligent_<br>Device | <u> </u>            |                                            | *1                                                                                                                                                | Intelligent device station sample code The sample code consists of the following program:  • User program (English comment version)  • CP520 driver main body  • CP520 driver interface functions (English comment version)  • CP520 driver callback functions (English comment version) IAR Embedded Workbench file (Compiler settings, link settings, build settings, etc.) |  |

|                        |                     |                                            | *1                                                                                                                                                | Intelligent device station sample code, IAR Embedded Workbench files (Japanese comment versions of the above)                                                                                                                                                                                                                                                                 |  |

| Remote_<br>Device      | English<br>Japanese | sample, driver, IAR<br>sample, driver, IAR | *1                                                                                                                                                | Remote device station sample code,<br>IAR Embedded Workbench files<br>(Same as for intelligent device station)                                                                                                                                                                                                                                                                |  |

| Manual                 |                     | drawing_CP520.<br>pdf                      | CP520 application circuit diagram examples<br>(reference circuit diagrams of CP520, CP520 peripheral<br>circuits, and CP520 power supply circuit) |                                                                                                                                                                                                                                                                                                                                                                               |  |

| _                      |                     |                                            | readme_e.txt                                                                                                                                      | Description of contents of enclosed CD-ROM (English)                                                                                                                                                                                                                                                                                                                          |  |

| -                      |                     | CP520_Softwar                              |                                                                                                                                                   | END-USER SOFTWARE LICENSE AGREEMENT (English)*2                                                                                                                                                                                                                                                                                                                               |  |

| -                      |                     | CP520_Softwar                              | END-USER SOFTWARE LICENSE AGREEMENT (Japanese)*2                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                               |  |

| -                      | -                   |                                            | readme_j.txt                                                                                                                                      | Description of contents of enclosed CD-ROM (Japanese)                                                                                                                                                                                                                                                                                                                         |  |

| _                      |                     | version.txt                                | Version information of enclosed CD-ROM                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                               |  |

<sup>\*1:</sup> For file names, refer to readme\_e.txt or readme\_j.txt.

<sup>\*2:</sup> Be sure to check the file.

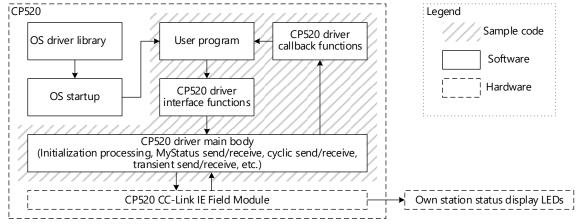

#### 1.5 Sample Code Overview

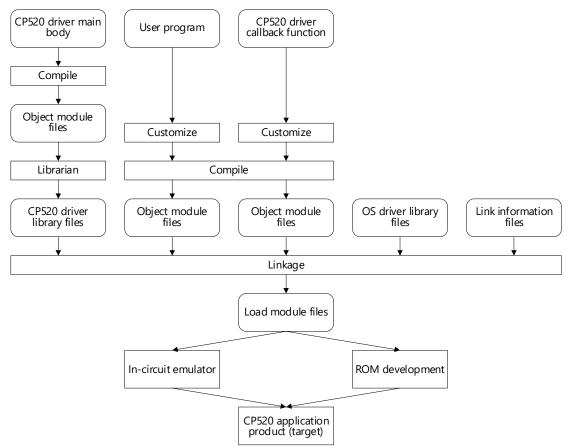

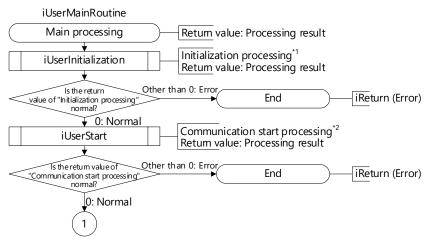

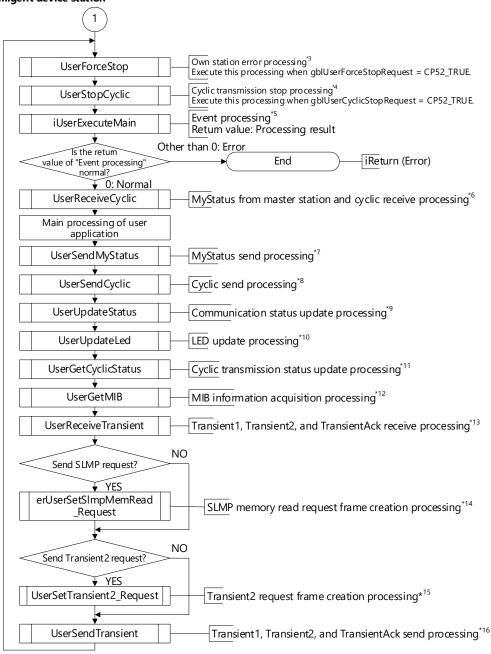

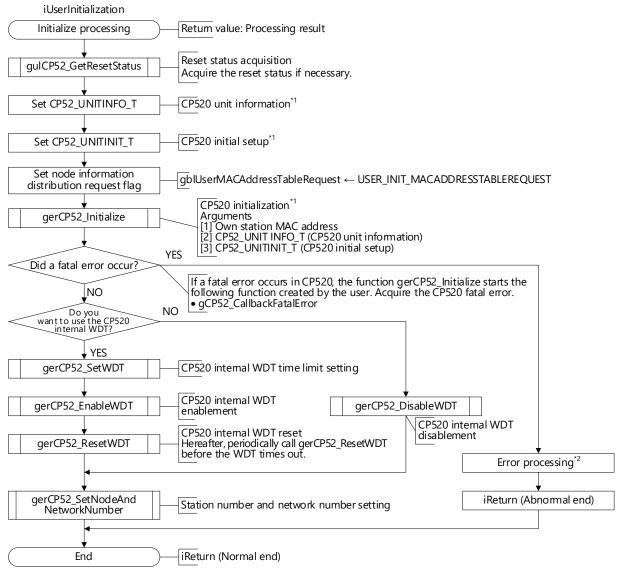

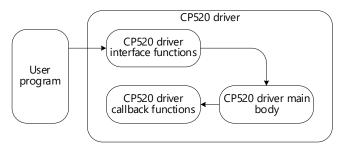

The sample code consists of the user program, CP520 driver interface functions, CP520 driver callback functions, and the CP520 driver main body.

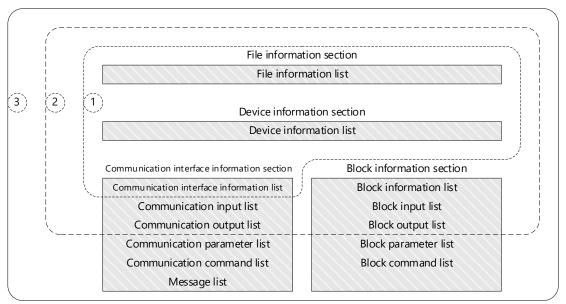

- \*: The sample code describes only the information related to CC-Link IE Field Network (communication function information).

- (1) The user program is an application program created by the user. The program in the sample code is provided for your reference for checking intelligent device station or remote device station logic. Customize the program in accordance with user requirement specifications. (Refer to Chapter 10 "CREATING USER PROGRAMS".)

- (2) CP520 driver interface functions are functions called when a CP520 driver function is used by the user program. Customization is not required. (Refer to Section 11.2 "CP520 Driver Interface Function List".)

- (3) CP520 driver callback functions describe examples of processing on the user program side in response to events that occur on the CP520 driver side. Customize the functions in accordance with user requirement specifications. (Refer to Section 11.4 "CP520 Driver Callback Function List".)

- (4) The CP520 driver main body is the main body of the driver area that is called by CP520 driver interface functions and controls CP520. Customization is not required.

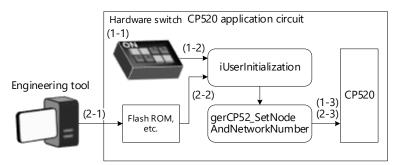

#### 1.6 System Configuration

#### (1) Software configuration

The following describes an example of the software configuration of a CP520 application product. With usage of the OS driver library\*1 and various functions provided by the CP520 driver, the user program can utilize various CP520 functions, such as cyclic transmission and transient transmission.

\*1: For details, refer to Section 2.5 "Preparing for Software Development".

Figure 1.6-1 Software Configuration Overview

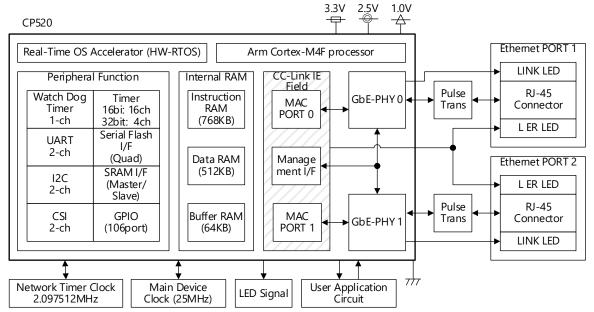

### (2) Hardware configuration

The following describes an example of the hardware configuration of a CP520 application product. The hardware consists of CP520, peripheral components, and two Ethernet ports. Note that the term "CPU" used in the following chapters refers to the areas other than GbE-PHY areas in CP520.

Figure 1.6-2 Hardware Configuration Overview

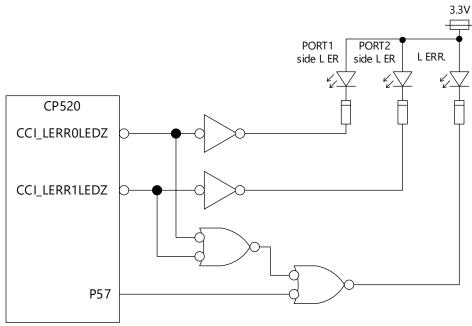

This manual identifies the GbE-PHY and LED signals connected to Ethernet Port 1 and Ethernet Port 2 using the numbering below.

| Ethernet PORT  | GbE-PHY  | LINK LED  | L ER LED      |

|----------------|----------|-----------|---------------|

| Ethernet PORT1 | GbE-PHY0 | PHY0_LED0 | CCI_LERR0LEDZ |

| Ethernet PORT2 | GbE-PHY1 | PHY1_LED0 | CCI_LERR1LEDZ |

## 1.7 Relationship with R-IN32M4-CL2

CP520 shares the same LSI functions and specifications as those of R-IN32M4-CL2 manufactured by Renesas Electronics Corporation.

## [Related documents]

The following documents may be used as reference for LSI functions and specifications.

Download the documents from the Renesas Electronics website (https://www.renesas.com/).

Note: The asterisks ("\*\*\*\*") at the end of each document number indicate the version.

Table 1.7-1 Renesas Electronics Related Documents

| Title                                            | Document No.    |

|--------------------------------------------------|-----------------|

| R-IN32M4-CL2 User's Manual                       | R18UZ0033EJ**** |

| R-IN32M4-CL2 User's Manual: Peripheral Modules   | R18UZ0035EJ**** |

| R-IN32M4-CL2 User's Manual: Board Design         | R18UZ0046EJ**** |

| R-IN32M4-CL2 Programming Manual: Driver          | R18UZ0038EJ**** |

| R-IN32M4-CL2 Programming Manual: OS              | R18UZ0040EJ**** |

| R-IN32M4-CL2 User's Manual: Gigabit Ethernet PHY | R18UZ0043EJ**** |

#### [Driver library]

The sample code provided in this manual describes only the information related to CC-Link IE Field Network (communication function information).

For CPU and peripheral functions, the driver library below is required.

Download the files from the Renesas Electronics website (https://www.renesas.com/).

Table 1.7-2 Renesas Electronics Driver Library

| Downloaded Product Name                     | File Name                               |

|---------------------------------------------|-----------------------------------------|

| Driver/Middleware Set for IAR KickStart Kit | an-r18an0031jj0240-r-in32m4-iar-bsp.zip |

#### [Arm Cortex-M4]

For the CPU functions and specifications, refer to the documents published by Arm Limited.

Download the documents from the Arm Limited website (https://www.arm.com/).

# 2 STUDYING AND PREPARING SPECIFICATIONS PRIOR TO DEVELOPMENT

This chapter describes the specifications to be investigated and preparations to be made when developing a CP520 application product.

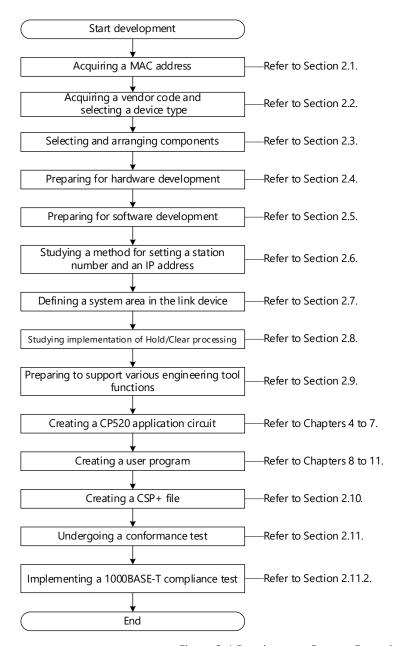

Figure 2-1 Development Process Example

#### 2.1 Acquiring a MAC Address

CP520 application products are Ethernet (IEEE 802.3ab) compliant. Be sure to acquire a MAC address MA-L (MAC Address Block Large) unique to the device to be developed.

To acquire a MAC address, contact the following authority (department) in the USA.

The IEEE Registration Authority

Website: https://standards.ieee.org/products-programs/regauth/ (March 2024)

### 2.2 Acquiring a Vendor Code and Selecting a Device Type

CP520 application products require registration of a vendor code and device type. The vendor code and device type are assigned and managed by the CC-Link Partner Association. If you have any questions, contact the CC-Link Partner Association.

Table 2.2-1 Vendor Code and Device Type

| Item         | Description                                                                                              |

|--------------|----------------------------------------------------------------------------------------------------------|

| Vendor code  | ID number (fifth to eighth digits) issued when the vendor joined the CC-Link Partner Association.        |

| (vendorCode) | For example, when the ID number is 123-456-7890, the vendor code will be 5678.                           |

| Device type  | Select the applicable device type from the "CC-Link IE Field Network Specification (Device Profile)". If |

| (deviceType) | an applicable device type does not exist, consult with the CC-Link Partner Association.                  |

### 2.3 Arranging Components

The components used in a CP520 application circuit are classified into CP520 and general components.

#### (1) CP520

CP520 can be ordered using the model names below. Purchase the product at a retail location that handles Mitsubishi Electric products.

Table 2.3-1 CP520 Model Names

| Product Name | Model         | Package Quantity | Manufacturer                    |

|--------------|---------------|------------------|---------------------------------|