## Programmable Controller

# CC-Link IE TSN FPGA Module User's Manual

- -NZ2GN2S-D41P01

- -NZ2GN2S-D41D01

- -NZ2GN2S-D41PD02

- -NZ2EX2S-D41P01

- -NZ2EX2S-D41D01

- -NZ2EX2S-D41A01

- -FPGA module configuration tool(SW1DNN-CCIETFLEXP-M)

## **SAFETY PRECAUTIONS**

(Read these precautions before using this product.)

Before using this product, please read this manual and the relevant manuals carefully and pay full attention to safety to handle the product correctly.

If the equipment is used in a manner not specified by the manufacturer, the protection provided by the equipment may be impaired.

The precautions given in this manual are concerned with this product only. For the safety precautions of the programmable controller system, refer to the user's manual for the CPU module used.

In this manual, the safety precautions are classified into two levels: " WARNING" and " CAUTION".

## **WARNING**

Indicates that incorrect handling may cause hazardous conditions, resulting in death or severe injury.

## **A** CAUTION

Indicates that incorrect handling may cause hazardous conditions, resulting in minor or moderate injury or property damage.

Under some circumstances, failure to observe the precautions given under "CAUTION" may lead to serious consequences.

Observe the precautions of both levels because they are important for personal and system safety.

Make sure that the end users read this manual and then keep the manual in a safe place for future reference.

### [Design Precautions]

## **WARNING**

- In the case of a communication failure in the network, data of the master station are held. Check Data link status (each station) (SW00B0 to SW00B7) and configure an interlock circuit in the program to ensure that the entire system will operate safely.

- Do not use any "use prohibited" signals as a remote input or output signal. These signals are reserved for system use. Do not write any data to the "use prohibited" areas in the remote register. If these operations are performed, an accident may occur due to an incorrect output or malfunction.

- Configure safety circuits external to the programmable controller to ensure that the entire system

operates safely even when a fault occurs in the external power supply or the programmable controller.

Failure to do so may result in an accident due to an incorrect output or malfunction.

- (1) Output status varies depending on the setting status of each function that controls digital output and analog output, or communication status with the CC-Link IE TSN master station. Therefore, configure settings carefully. For details on the output status, refer to Page 315 FPGA Control Function.

- (2) Signals may not be output correctly if an output element or its internal circuit has a failure.

Configure an external circuit for monitoring output signals that could cause a serious accident.

- Incorporate safety circuits in a user circuit of the FPGA so that the entire system will operate safely (for instance, by holding signal output) even when an error occurs in the user circuit of the FPGA.

Failure to do so may result in an accident due to an incorrect output or malfunction.

- Do not change standard circuits because the FPGA control function is incorporated in the FPGA as safety circuits.

- After verification of the FPGA design, verify actual module operations before putting the module in the system.

### [Design Precautions]

## **A**CAUTION

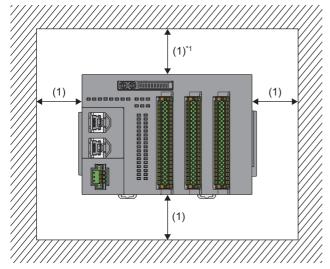

- Do not install the communication cables together with the main circuit lines or power cables. Keep a

distance of 100mm or more between them. Failure to do so may result in malfunction due to noise.

- Do not install the control lines together with the main circuit lines or power cables. Keep a distance of 150mm or more between them. Failure to do so may result in malfunction due to noise.

- At on/off of the power, a large voltage may occur or a large current may flow between output terminals for a moment. In this case, start the control after analog outputs become stable.

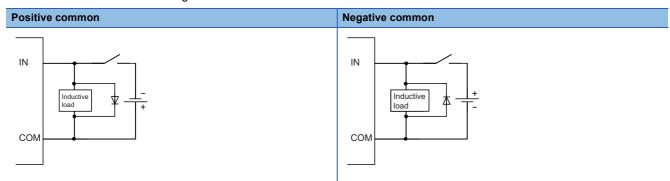

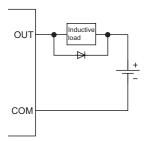

- During control of an inductive load such as a lamp, heater, or solenoid valve, a large current (approximately ten times greater than normal) may flow when the output is turned from off to on. Therefore, use a module that has a sufficient current rating.

### [Security Precautions]

## **WARNING**

- To maintain the security (confidentiality, integrity, and availability) of the programmable controller and the system against unauthorized access, denial-of-service (DoS) attacks, computer viruses, and other cyberattacks from external devices via the network, take appropriate measures such as firewalls, virtual private networks (VPNs), and antivirus solutions.

- Configuration data can be written to this product via a JTAG port by using a dedicated cable for FPGA download. To prevent configuration data from accidentally being written to the product, except for the purpose of FPGA download, lock the control panel so that only qualified maintenance personnel can operate it.

### [Installation Precautions]

## **WARNING**

Shut off the external power supply (all phases) used in the system before mounting or removing a module. Failure to do so may result in electric shock or cause the module to fail or malfunction.

## [Installation Precautions]

## **ACAUTION**

- Use the module in an environment that meets the descriptions of Page 32 General Specifications in this manual. Failure to do so may result in electric shock, fire, malfunction, or damage to or deterioration of the product.

- Do not directly touch any conductive parts and electronic components of the module. Doing so can cause malfunction or failure of the module.

- Securely connect the cable connectors. Poor contact may cause malfunction.

- Beware that the module could be very hot while power is on and immediately after power-off.

### [Wiring Precautions]

### **!** WARNING

Shut off the external power supply (all phases) used in the system before wiring. Failure to do so may result in electric shock or cause the module to fail or malfunction.

### [Wiring Precautions]

## **⚠** CAUTION

- Individually ground the FG terminal of the programmable controller with a ground resistance of 100 ohms or less. Failure to do so may result in electric shock or malfunction.

- Check the rated voltage and terminal layout before wiring to the module, and connect the cables correctly. Connecting a power supply with a different voltage rating or incorrect wiring may cause a fire or failure.

- Prevent foreign matter such as dust or wire chips from entering the module. Such foreign matter can cause a fire, failure, or malfunction.

- Place the cables in a duct or clamp them. If not, dangling cables may swing or inadvertently be pulled, resulting in malfunction or damage to modules or cables. In addition, the weight of the cables may put stress on modules in an environment of strong vibrations and shocks.

- Do not install the communication cables together with the main circuit lines or power cables. Keep a distance of 100mm or more between them. Failure to do so may result in malfunction due to noise.

- Do not install the control lines together with the main circuit lines or power cables. Keep a distance of 150mm or more between them. Failure to do so may result in malfunction due to noise.

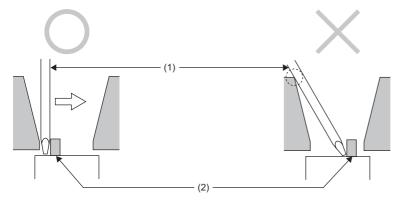

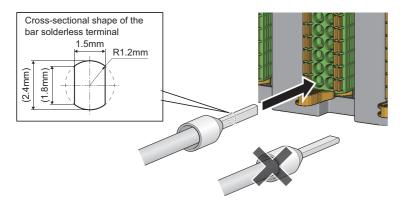

- When disconnecting the cable from the module, do not pull the cable by the cable part. For the cable with connector, hold the connector part of the cable. For the cable connected to the terminal block, pull the cable while pressing the release button using a flathead screwdriver with a tip width of 2.0 to 2.5mm. Pulling the cable without pressing the release button may result in malfunction or damage to the module or cable.

- When an overcurrent caused by an error of an external device or a failure of the programmable controller flows for a long time, it may cause smoke and fire. To prevent this, configure an external safety circuit, such as a fuse.

- Mitsubishi programmable controllers must be installed in control panels. Wiring and replacement of a module must be performed by qualified maintenance personnel with knowledge of protection against electric shock. For wiring methods, refer to Page 66 Wiring.

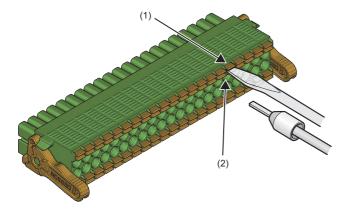

### [Startup and Maintenance Precautions]

## **WARNING**

- Do not touch any terminal while power is on. Doing so will cause electric shock or malfunction.

- Shut off the external power supply (all phases) used in the system before cleaning the module or retightening the terminal block screws or connector screws. Failure to do so may cause the module to fail or malfunction.

### [Startup and Maintenance Precautions]

## **A**CAUTION

- Do not disassemble or modify the module. Doing so may cause failure, malfunction, injury, or a fire.

- Do not drop or apply strong shock to the module. Doing so may damage the module.

- Use any radio communication device such as a cellular phone or PHS (Personal Handy-phone System) 25cm or more away in all directions from the programmable controller. Failure to do so may cause malfunction.

- Shut off the external power supply (all phases) used in the system before mounting or removing a module. Failure to do so may cause the module to fail or malfunction.

- After the first use of the product, do not connect/remove the extension module to/from the main module, and do not mount/remove the terminal block or connector to/from the modules more than 50 times (IEC 61131-2/JIS B 3502 compliant). Exceeding the limit may cause malfunction.

- The operation of IP address/station number setting switches must be limited to 10000 times per switch. Exceeding the limit may cause malfunction.

- The operation of function setting switches must be limited to 1000 times per switch. Exceeding the limit may cause malfunction.

- Before handling the module or cables to be connected to the module, touch a conducting object such as a grounded metal to discharge the static electricity from the human body. Wearing a grounded antistatic wrist strap is recommended. Failure to discharge the static electricity may cause the module to fail or malfunction.

- Startup and maintenance of a control panel must be performed by qualified maintenance personnel with knowledge of protection against electric shock. Lock the control panel so that only qualified maintenance personnel can operate it.

### [Disposal Precautions]

When disposing of this product, treat it as industrial waste.

### **CONDITIONS OF USE FOR THE PRODUCT**

- (1) MELSEC programmable controller ("the PRODUCT") shall be used in conditions;

- i) where any problem, fault or failure occurring in the PRODUCT, if any, shall not lead to any major or serious accident; and

- ii) where the backup and fail-safe function are systematically or automatically provided outside of the PRODUCT for the case of any problem, fault or failure occurring in the PRODUCT.

- (2) The PRODUCT has been designed and manufactured for the purpose of being used in general industries.

MITSUBISHI ELECTRIC SHALL HAVE NO RESPONSIBILITY OR LIABILITY (INCLUDING, BUT NOT LIMITED TO ANY AND ALL RESPONSIBILITY OR LIABILITY BASED ON CONTRACT, WARRANTY, TORT, PRODUCT LIABILITY) FOR ANY INJURY OR DEATH TO PERSONS OR LOSS OR DAMAGE TO PROPERTY CAUSED BY the PRODUCT THAT ARE OPERATED OR USED IN APPLICATION NOT INTENDED OR EXCLUDED BY INSTRUCTIONS, PRECAUTIONS, OR WARNING CONTAINED IN MITSUBISHI ELECTRIC USER'S, INSTRUCTION AND/OR SAFETY MANUALS, TECHNICAL BULLETINS AND GUIDELINES FOR the PRODUCT. ("Prohibited Application")

Prohibited Applications include, but not limited to, the use of the PRODUCT in;

- Nuclear Power Plants and any other power plants operated by Power companies, and/or any other cases in which the public could be affected if any problem or fault occurs in the PRODUCT.

- Railway companies or Public service purposes, and/or any other cases in which establishment of a special quality assurance system is required by the Purchaser or End User.

- Aircraft or Aerospace, Medical applications, Train equipment, transport equipment such as Elevator and Escalator, Incineration and Fuel devices, Vehicles, Manned transportation, Equipment for Recreation and Amusement, and Safety devices, handling of Nuclear or Hazardous Materials or Chemicals, Mining and Drilling, and/or other applications where there is a significant risk of injury to the public or property.

- Notwithstanding the above restrictions, Mitsubishi Electric may in its sole discretion, authorize use of the PRODUCT in one or more of the Prohibited Applications, provided that the usage of the PRODUCT is limited only for the specific applications agreed to by Mitsubishi Electric and provided further that no special quality assurance or fail-safe, redundant or other safety features which exceed the general specifications of the PRODUCTs are required. For details, please contact the Mitsubishi Electric representative in your region.

- (3) Mitsubishi Electric shall have no responsibility or liability for any problems involving programmable controller trouble and system trouble caused by DoS attacks, unauthorized access, computer viruses, and other cyberattacks.

## **INTRODUCTION**

Thank you for purchasing the CC-Link IE TSN FPGA module (hereafter abbreviated as FPGA module).

This manual describes the procedures, system configuration, parameter settings, functions, and troubleshooting of the relevant products listed below.

Before using this product, please read this manual and the relevant manuals carefully and develop familiarity with the functions and performance of the FPGA module to handle the product correctly.

When applying the program examples provided in this manual to an actual system, ensure the applicability and confirm that it will not cause system control problems.

Note that the menu names and operating procedures may differ depending on an operating system in use and its version. When reading this manual, replace the names and procedures with the applicable ones as necessary.

### Relevant products

NZ2GN2S-D41P01, NZ2GN2S-D41D01, NZ2GN2S-D41PD02, NZ2EX2S-D41A01, NZ2EX2S-D41P01, NZ2EX2S-D41D01

## **FPGA DEVELOPMENT SOFTWARE**

For FPGA development software (Intel<sup>®</sup> Quartus Prime), use the product with the software version 20.1.1, which (its operation) has been verified by Mitsubishi Electric. (FP Page 26 FPGA development software)

## **CONTENTS**

| SAFI | ETY PRECAUTIONS                                    |    |

|------|----------------------------------------------------|----|

| CON  | NDITIONS OF USE FOR THE PRODUCT                    |    |

|      | RODUCTION                                          |    |

| FPG. | SA DEVELOPMENT SOFTWARE                            |    |

| RELI | EVANT MANUALS                                      |    |

|      | RMS                                                |    |

|      | NERIC TERMS AND ABBREVIATIONS                      |    |

| PΑ   | ART 1 OVERVIEW                                     |    |

| CHA  | APTER 1 WHAT THIS MODULE CAN DO                    | 18 |

| CHA  | APTER 2 PRODUCT LINEUP                             | 21 |

| 2.1  | List of Products                                   | 21 |

| CHA  | APTER 3 SYSTEM CONFIGURATION                       | 23 |

| 3.1  | Applicable Systems                                 |    |

| PΑ   | ART 2 SPECIFICATIONS                               |    |

| CHA  | APTER 4 PART NAMES                                 | 28 |

| CHA  | APTER 5 SPECIFICATIONS                             | 32 |

| 5.1  | General Specifications                             |    |

| 5.2  | Performance Specifications                         |    |

|      | Common to the modules                              |    |

|      | Main module                                        |    |

|      | Extension module                                   |    |

| 5.3  | Ethernet Communication Specifications              |    |

| 5.4  | FPGA Performance                                   |    |

| PΑ   | ART 3 START-UP PROCEDURES                          |    |

| CHA  | APTER 6 PROCEDURES BEFORE OPERATION                | 52 |

| CHA  | APTER 7 INSTALLATION AND WIRING                    | 54 |

| 7.1  | Setting Switches                                   | 54 |

|      | IP address/station number setting switch setting   |    |

|      | Setting the function setting switches              | 58 |

| 7.2  | Installation Environment and Installation Position | 60 |

|      | Installation environment                           |    |

|      | Installation position                              |    |

|      | Installation orientation                           |    |

| 7.3  | Installation                                       |    |

|      | Connecting an extension module                     |    |

|     | How to mount a module on a DIN rail                        |     |

|-----|------------------------------------------------------------|-----|

| 7.4 | Wiring                                                     |     |

|     | Wiring to terminal block for module power supply and FG    |     |

|     | Ethernet cables                                            |     |

|     | Wiring to I/O terminal block                               |     |

| 7.5 | External Wiring                                            |     |

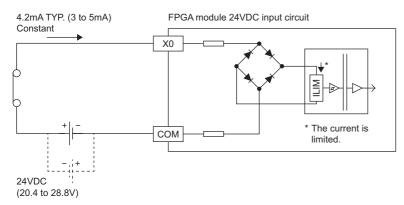

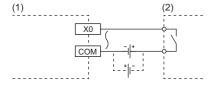

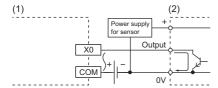

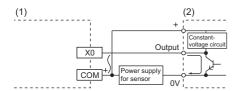

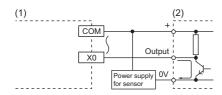

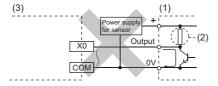

|     | DC input wiring                                            |     |

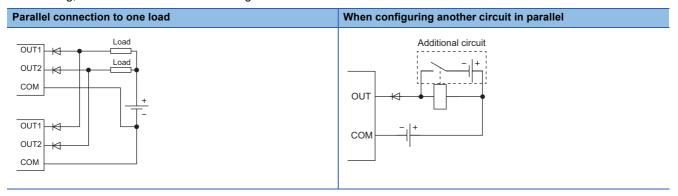

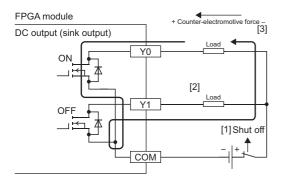

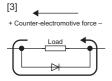

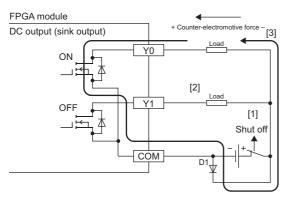

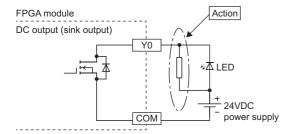

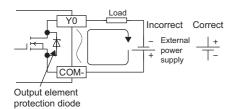

|     | Transistor output wiring                                   |     |

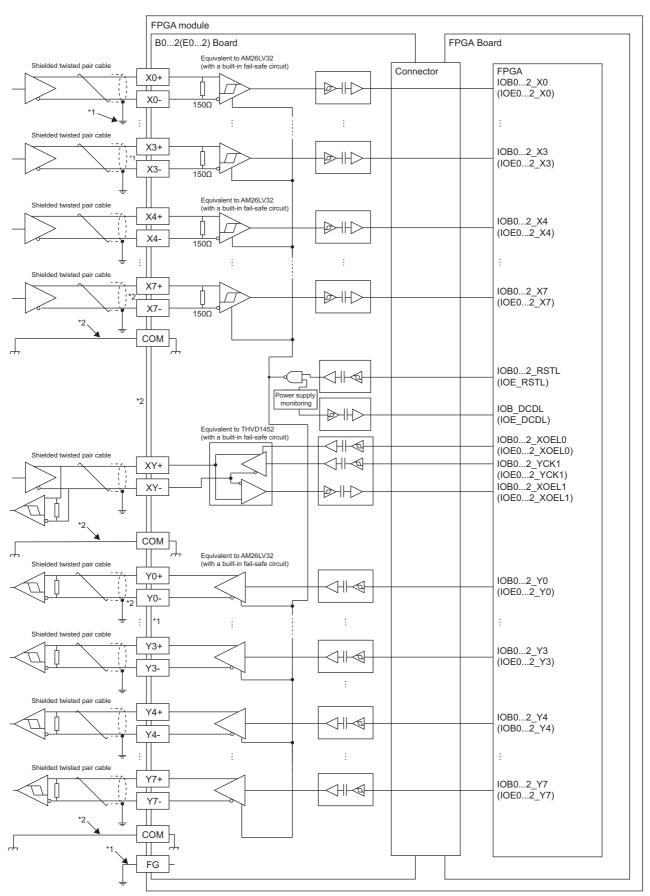

|     | Differential input/output wiring                           |     |

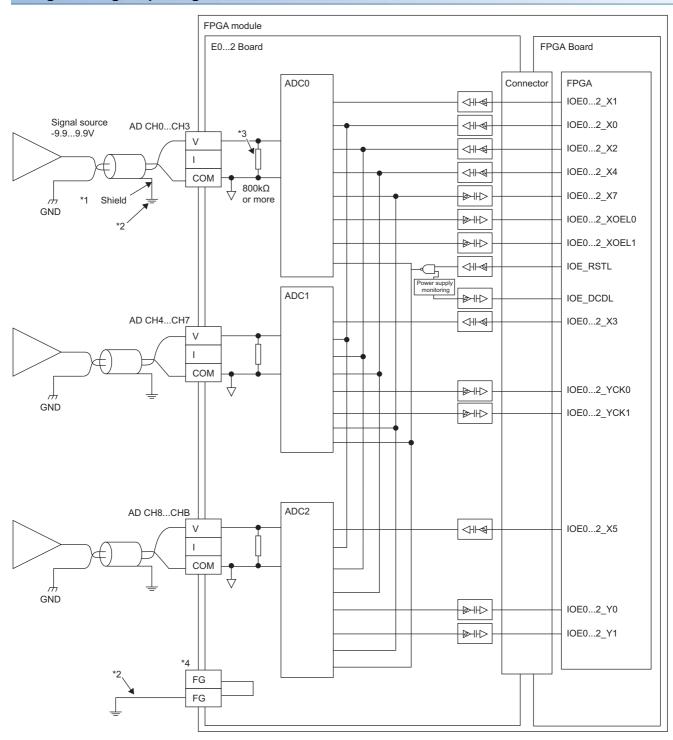

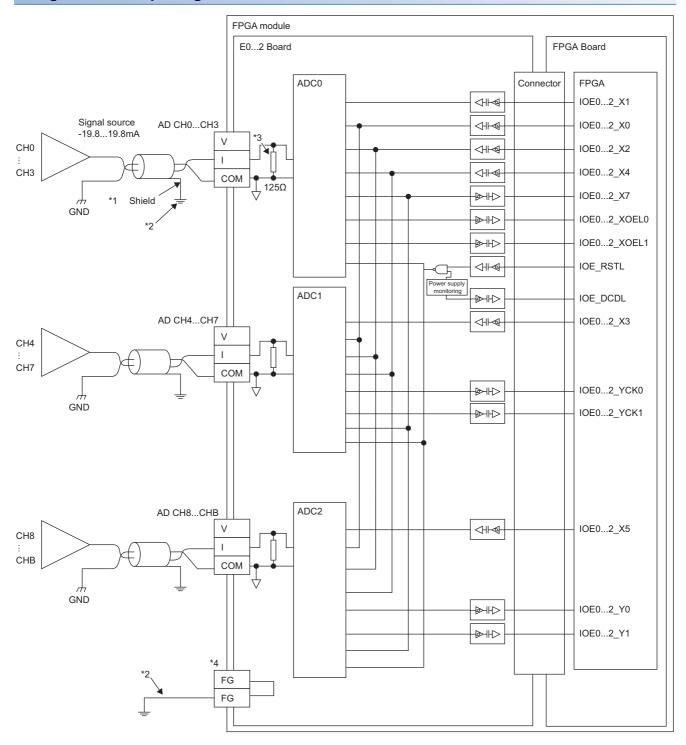

|     | Analog input wiring                                        |     |

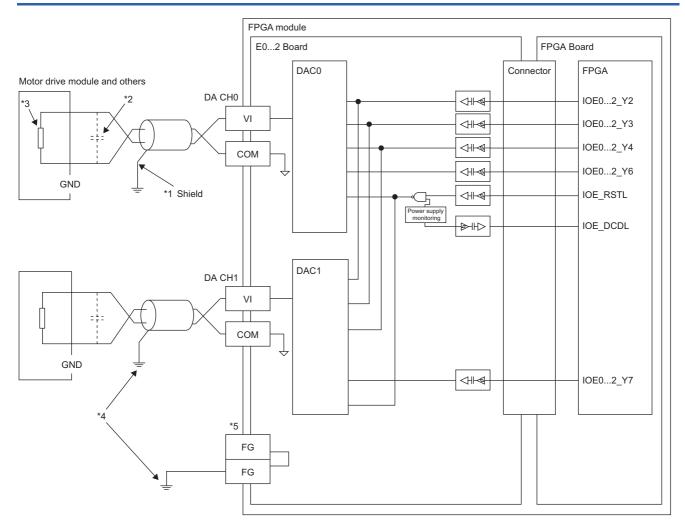

|     | Analog output wiring                                       |     |

|     | Analog output willing                                      |     |

| PΑ  | ART 4 SETTINGS                                             |     |

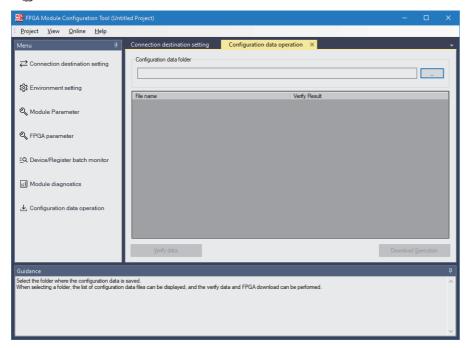

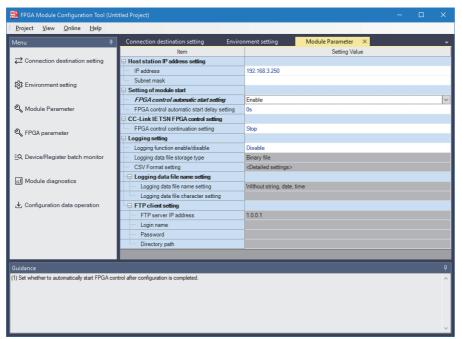

| CHA | APTER 8 FPGA MODULE CONFIGURATION TOOL                     | 86  |

| 8.1 | Starting Up and Finishing                                  | 86  |

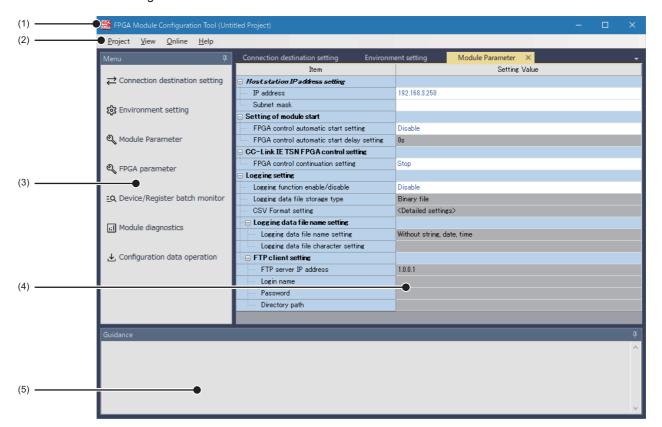

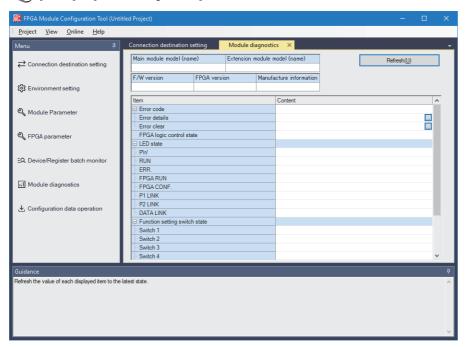

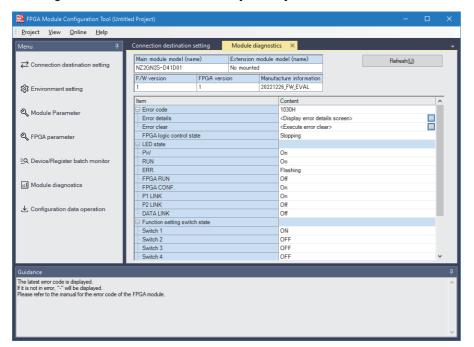

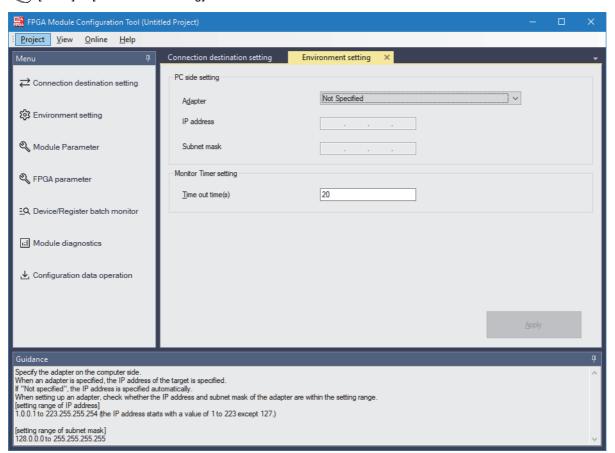

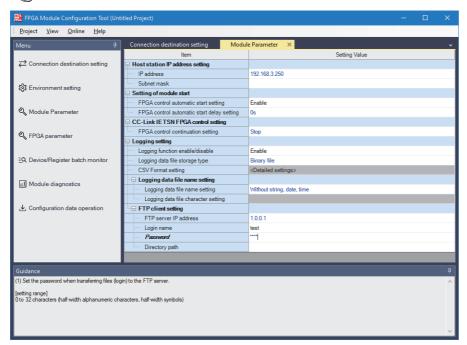

| 8.2 | Window Configuration                                       |     |

|     | Menu window                                                |     |

|     | Work window                                                | 90  |

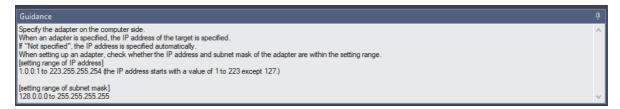

|     | Guidance window                                            |     |

| 8.3 | FPGA Module Configuration Tool Menu List                   |     |

| 8.4 | Project Function                                           |     |

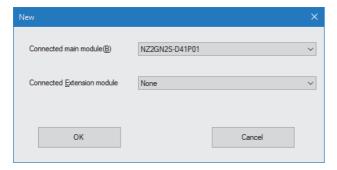

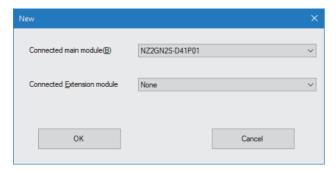

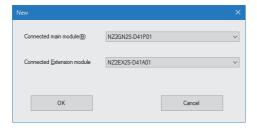

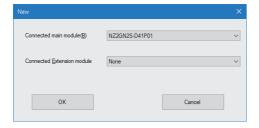

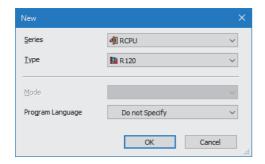

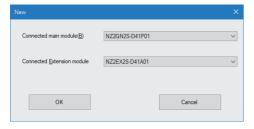

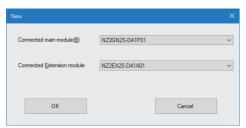

|     | Creating new projects                                      |     |

|     | Opening a project                                          |     |

|     | Saving the project                                         |     |

| 8.5 | Display Function                                           |     |

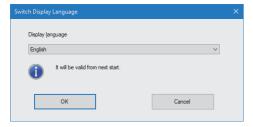

|     | Display language switching                                 |     |

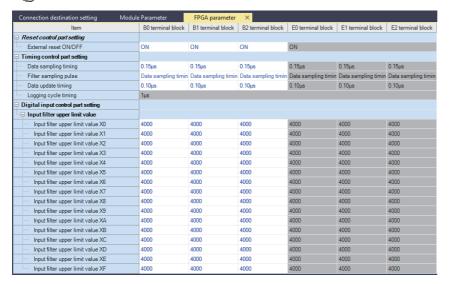

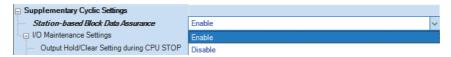

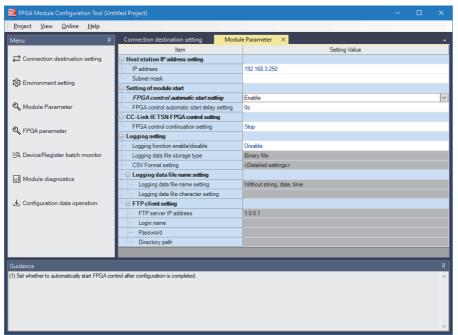

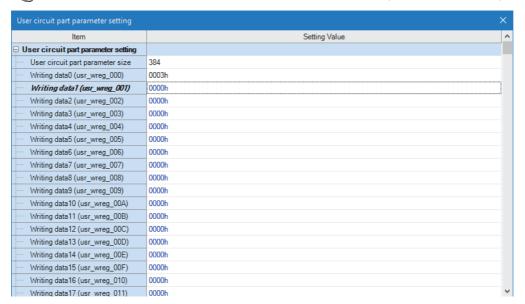

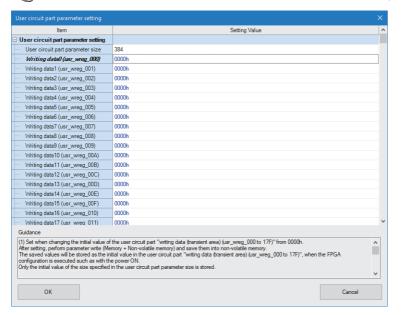

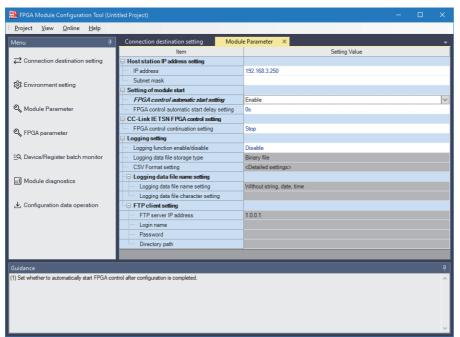

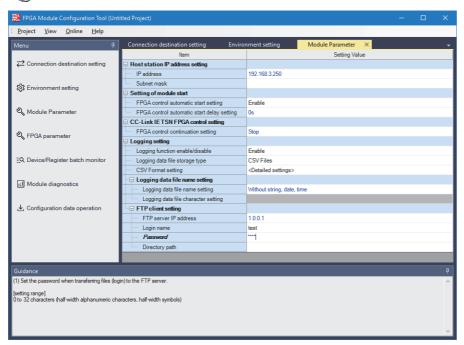

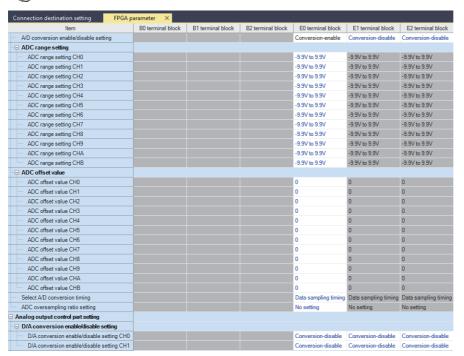

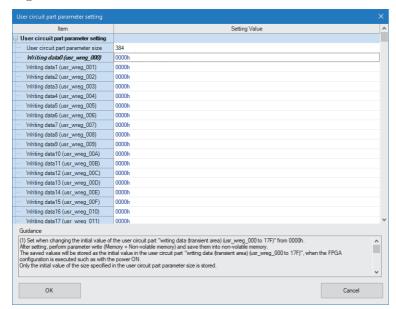

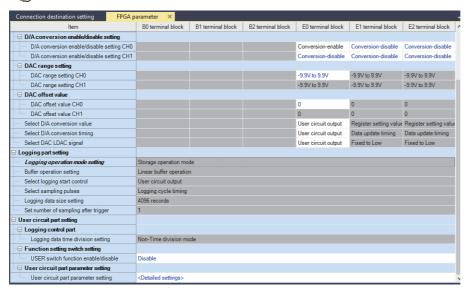

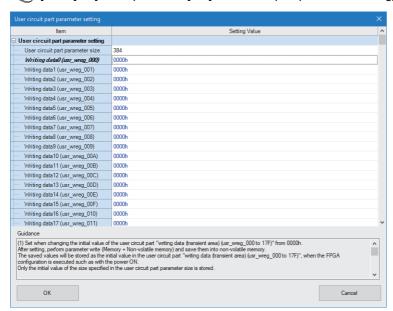

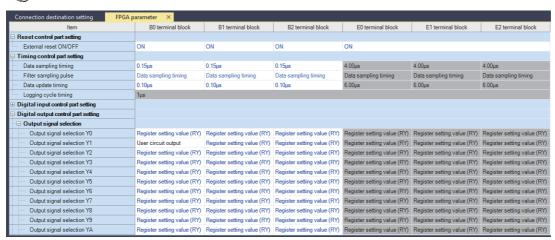

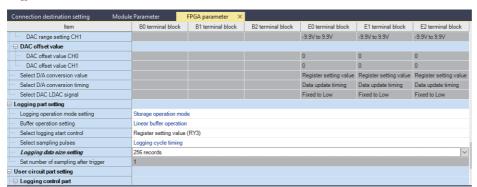

| 8.6 | Parameter Setting Function                                 |     |

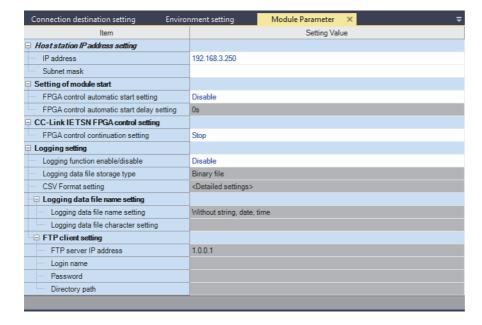

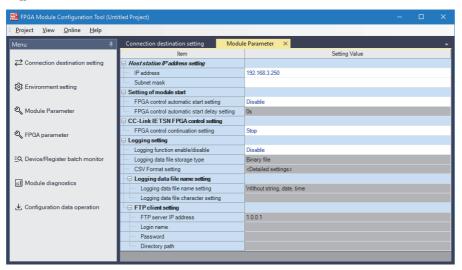

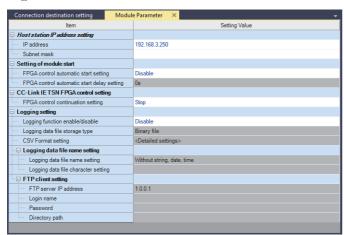

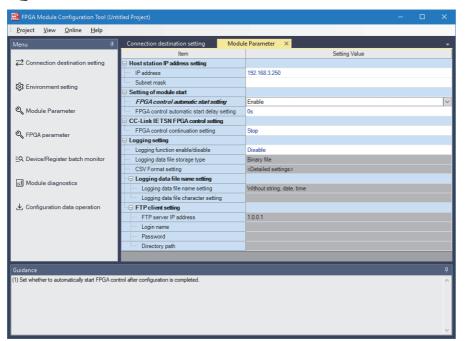

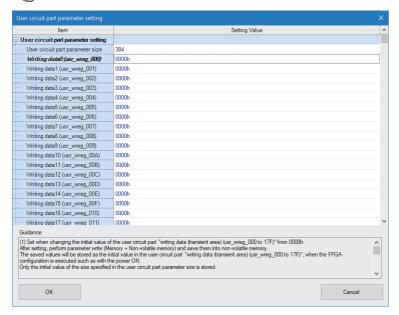

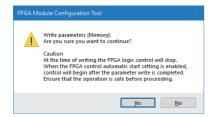

|     | Module parameters                                          |     |

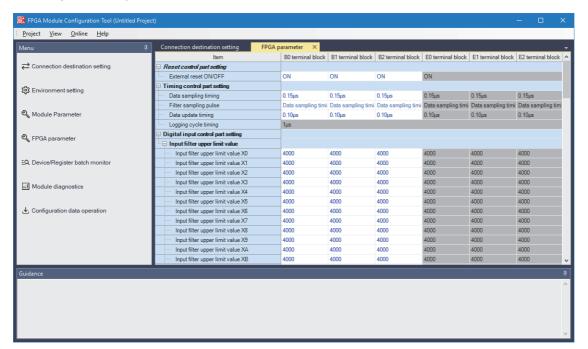

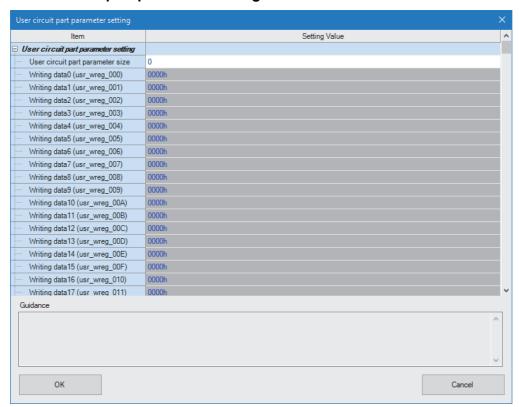

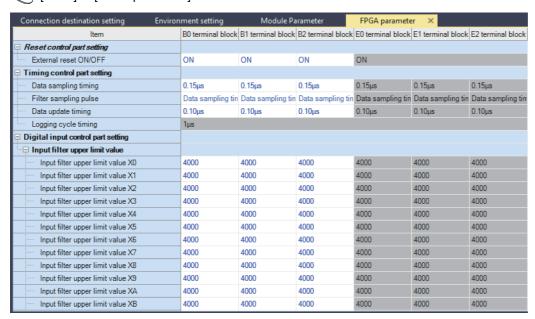

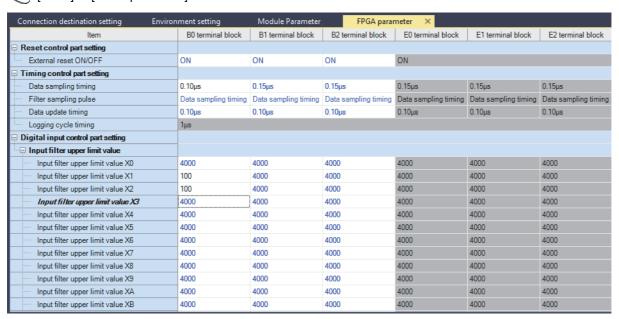

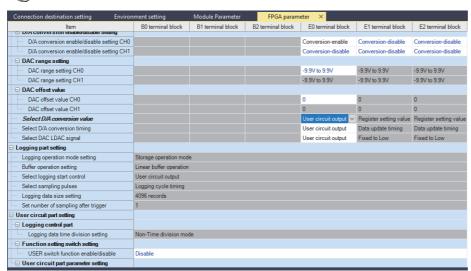

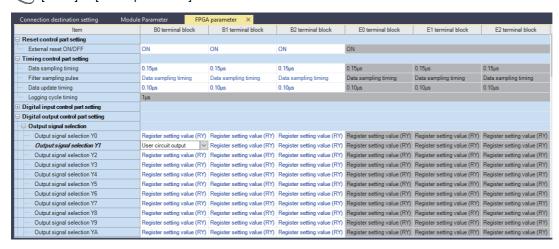

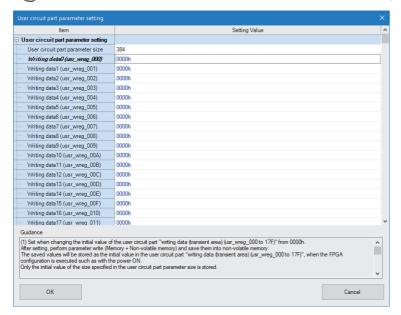

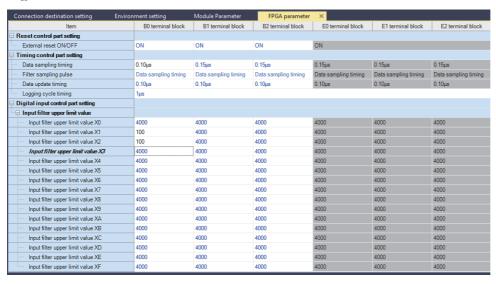

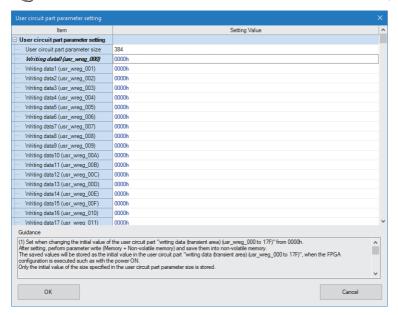

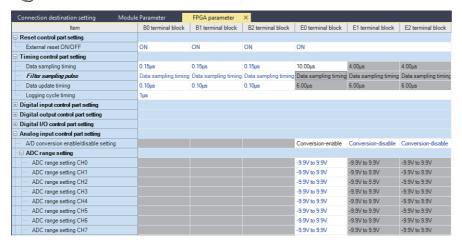

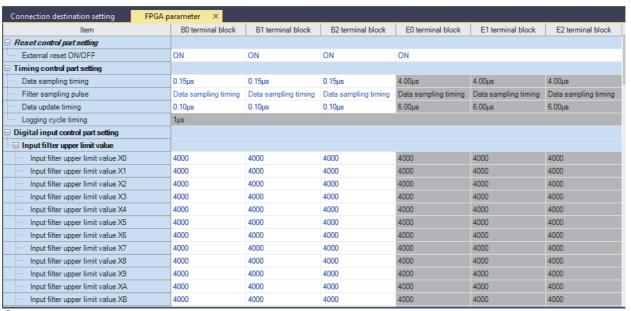

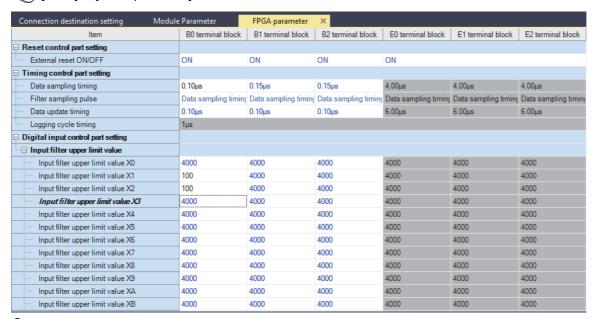

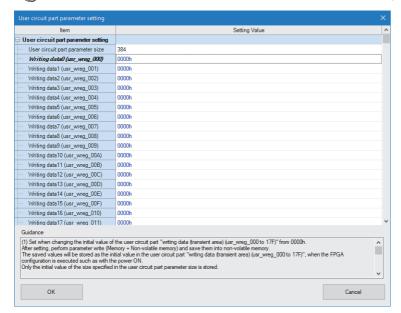

|     | FPGA parameters                                            |     |

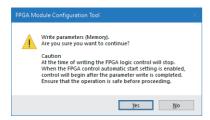

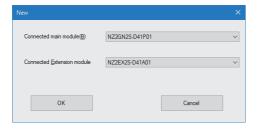

| 8.7 | Online Functions                                           |     |

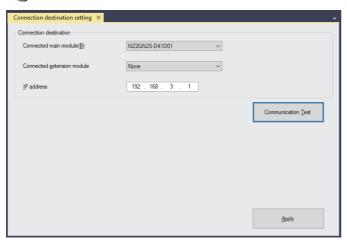

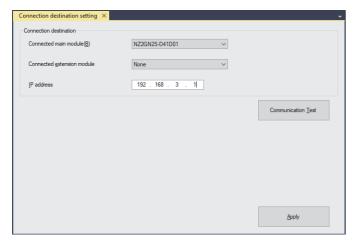

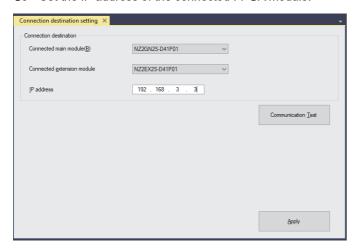

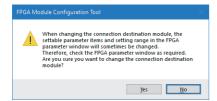

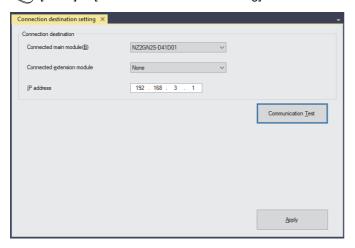

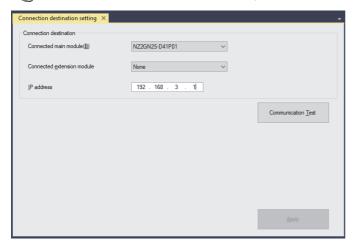

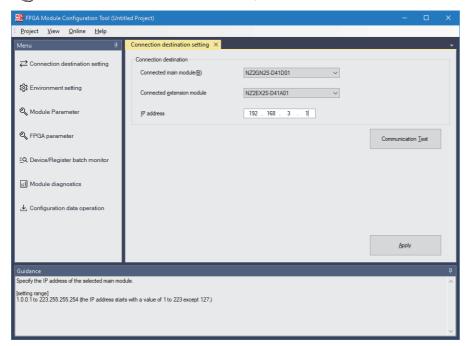

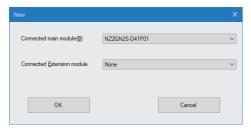

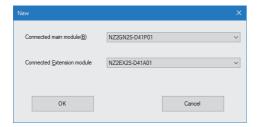

| •   | Connection destination setting                             |     |

|     | Communication test.                                        |     |

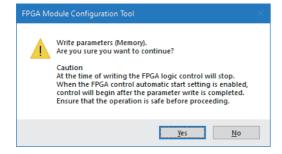

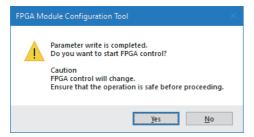

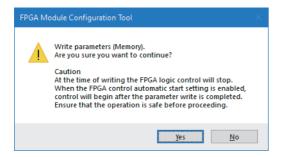

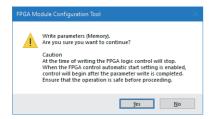

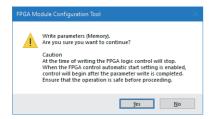

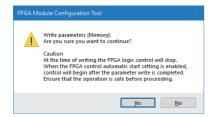

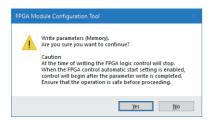

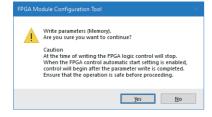

|     | Parameter writing                                          |     |

|     | Parameter read                                             |     |

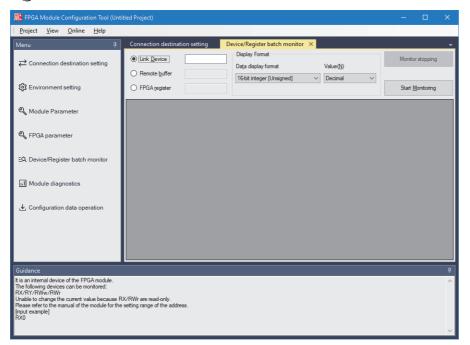

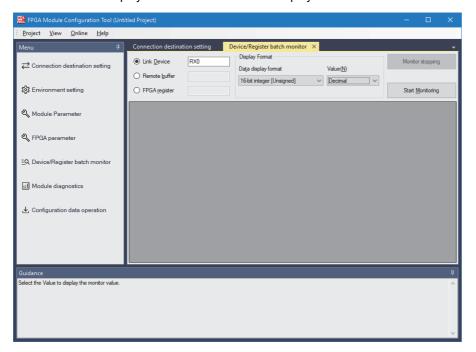

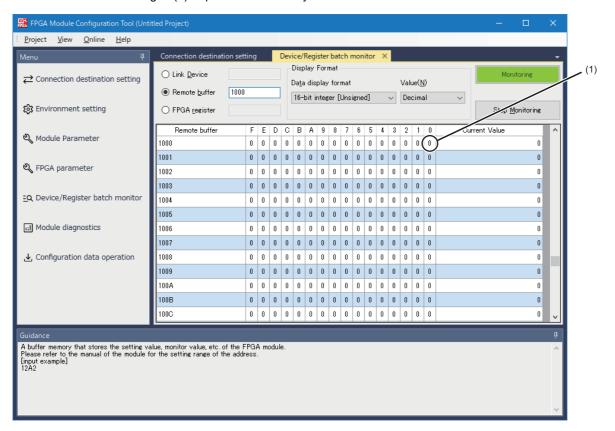

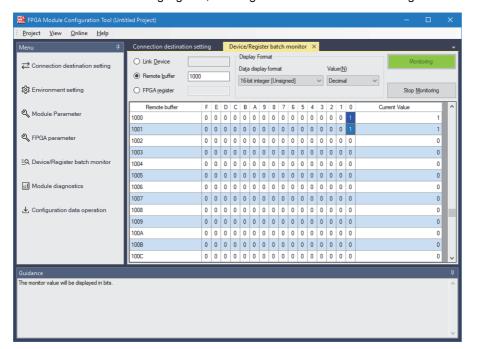

|     | Batch monitor display                                      |     |

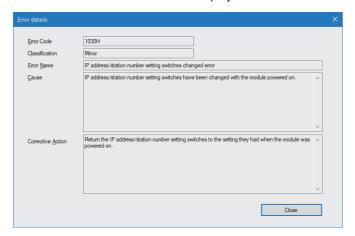

|     | Module diagnostics                                         |     |

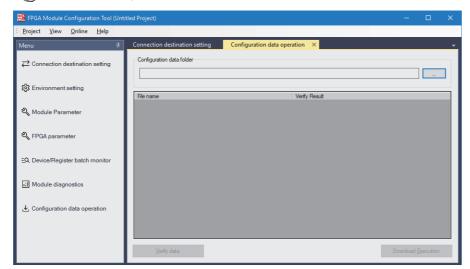

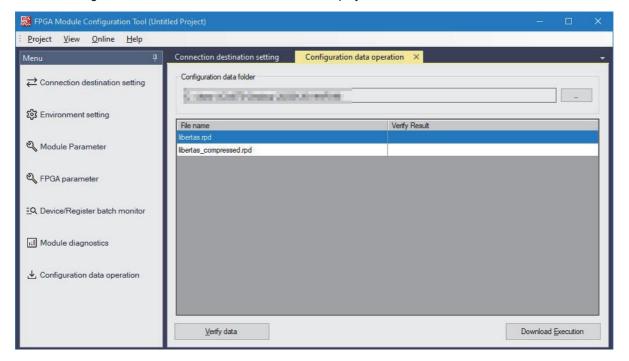

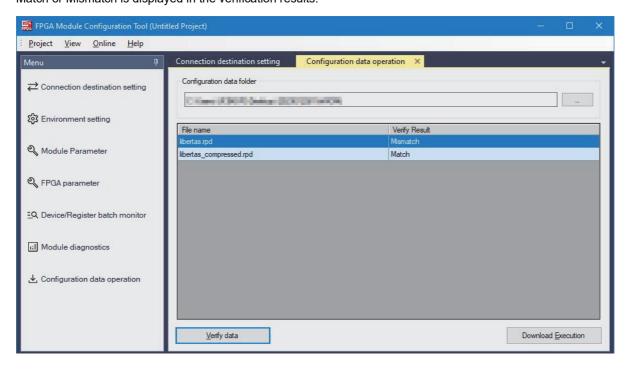

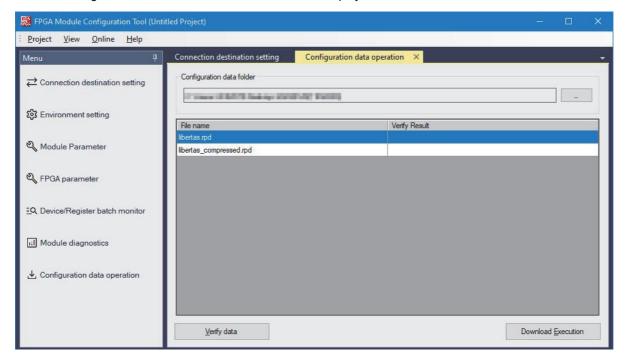

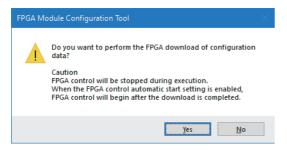

|     | Configuration data operation                               |     |

| 8.8 | Optional Functions                                         |     |

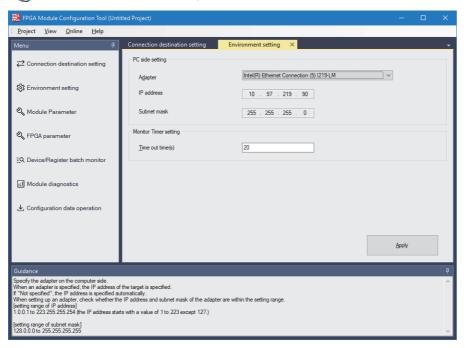

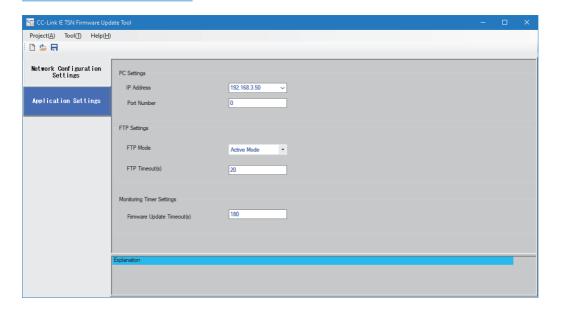

| 0.0 | Environment setting.                                       |     |

| ۰.  | Help Function.                                             |     |

| 8.9 | -                                                          |     |

|     | Checking the version of the FPGA Module Configuration Tool |     |

| CH  | APTER 9 PARAMETER SETTING                                  | 129 |

| 9.1 | For Standalone Mode                                        |     |

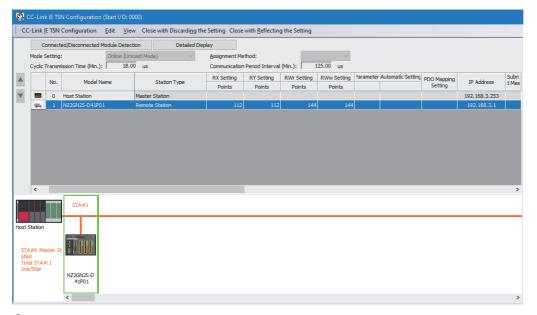

| 9.2 | For CC-Link IE TSN Communication Mode                      | 132 |

## PART 5 FPGAs

| CHA  | APTER 10 FPGA DEVELOPMENT                                             | 140 |

|------|-----------------------------------------------------------------------|-----|

| 10.1 | FPGA Development Procedures                                           | 140 |

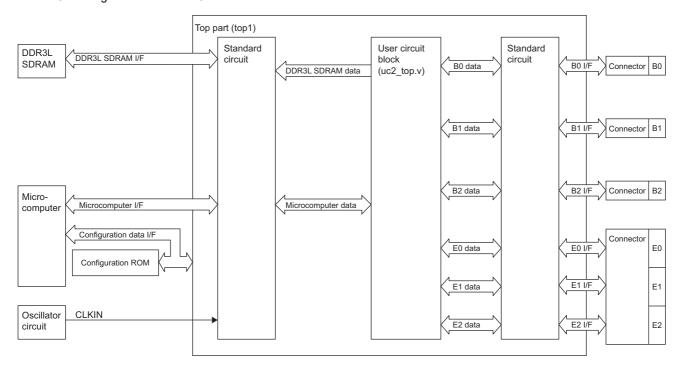

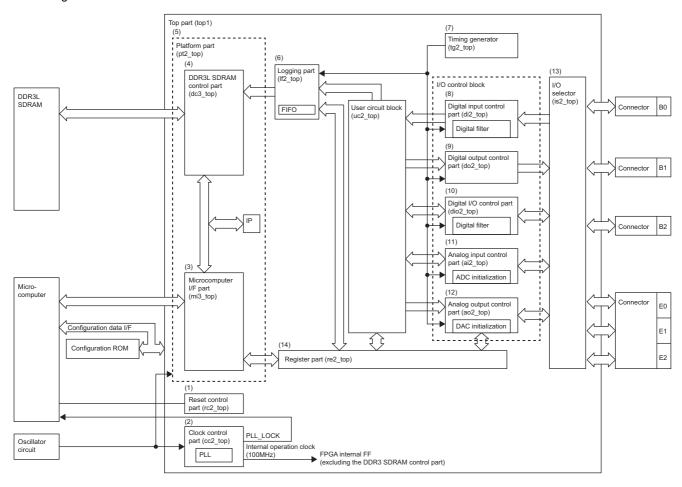

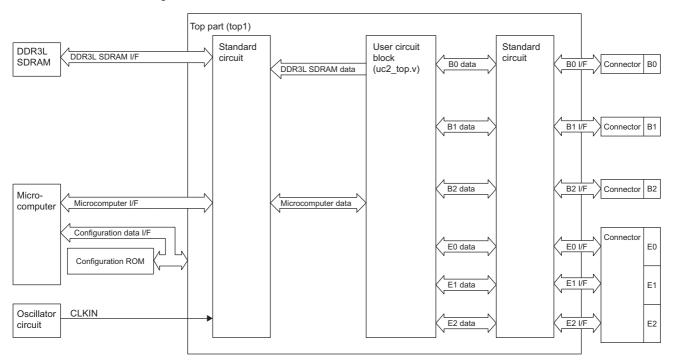

|      | Standard circuit block                                                | 141 |

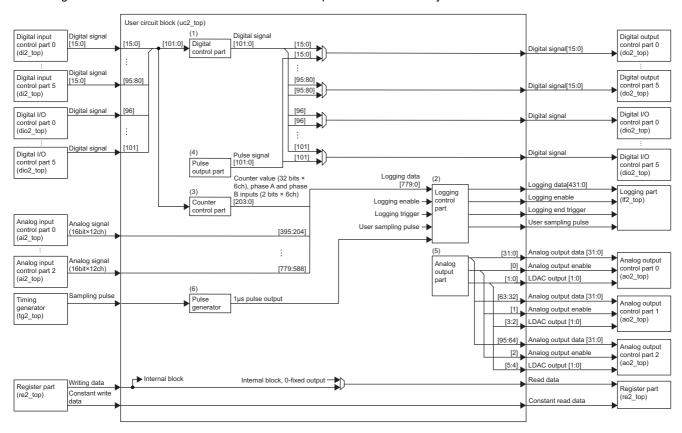

|      | User circuit block                                                    | 143 |

| 10.2 | FPGA Design Procedures                                                | 145 |

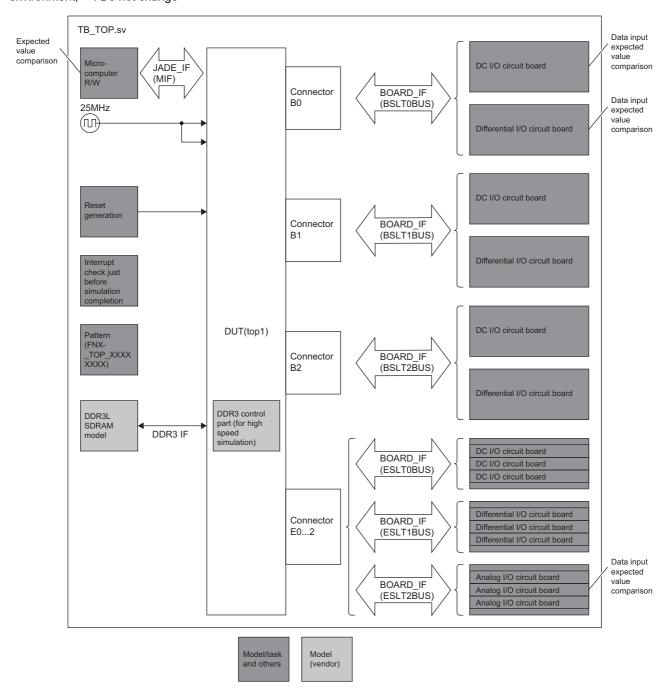

| 10.3 | FPGA Verification Procedure                                           | 146 |

| 10.4 | FPGA Logic Synthesis Procedures                                       | 174 |

| CHA  | APTER 11 FPGA INTERNAL CIRCUIT                                        | 177 |

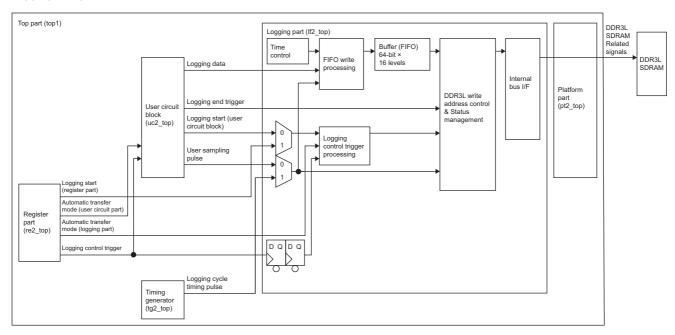

| 11.1 | Overview                                                              |     |

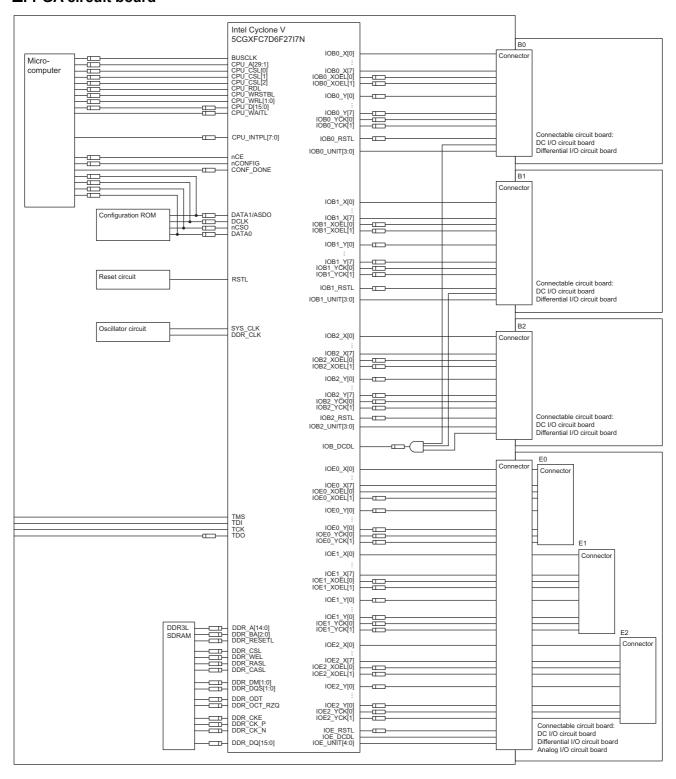

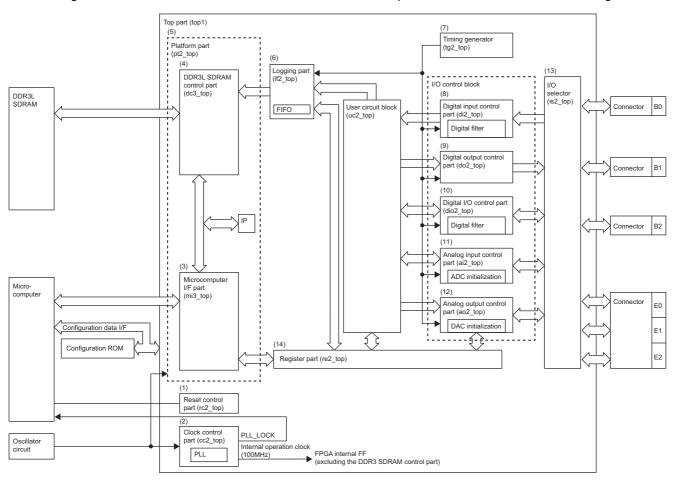

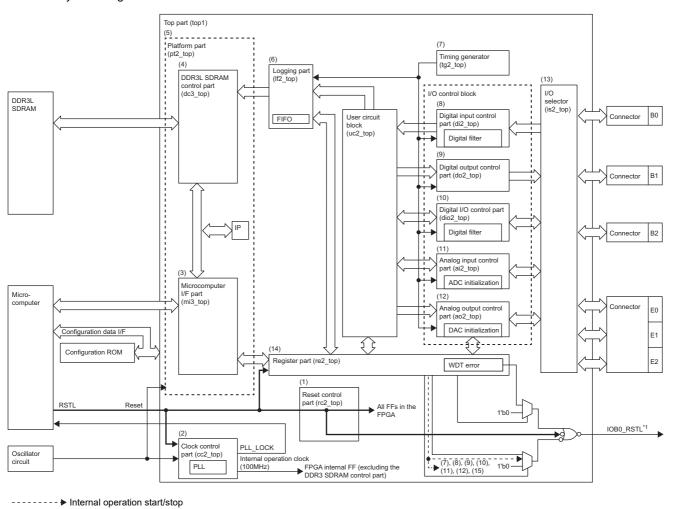

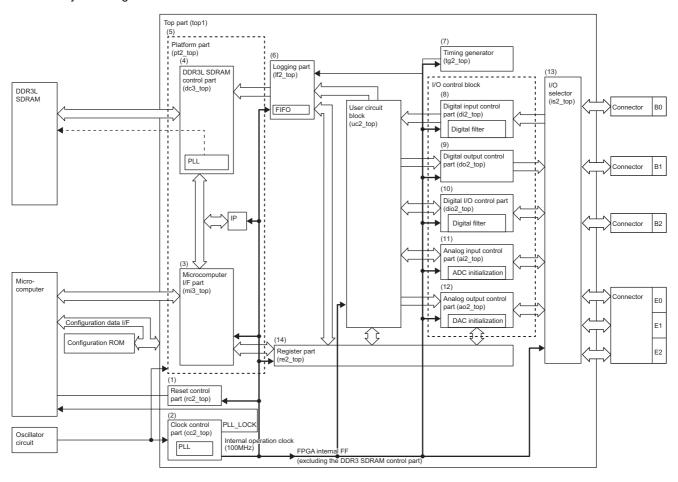

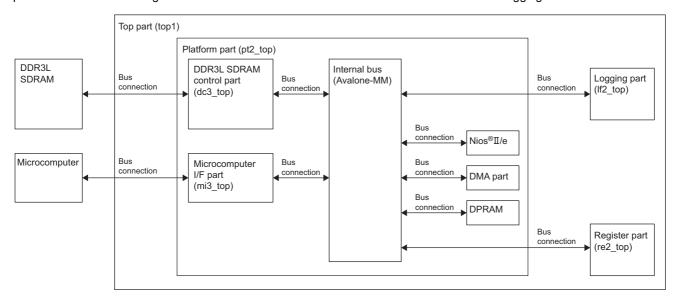

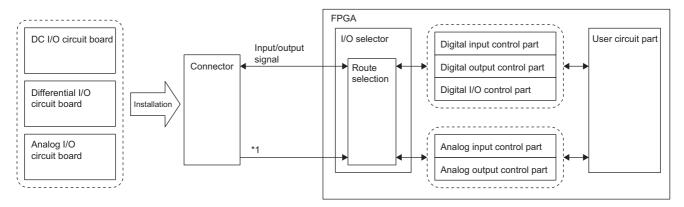

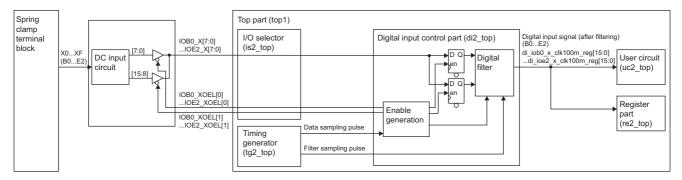

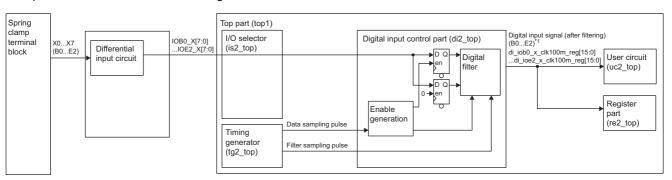

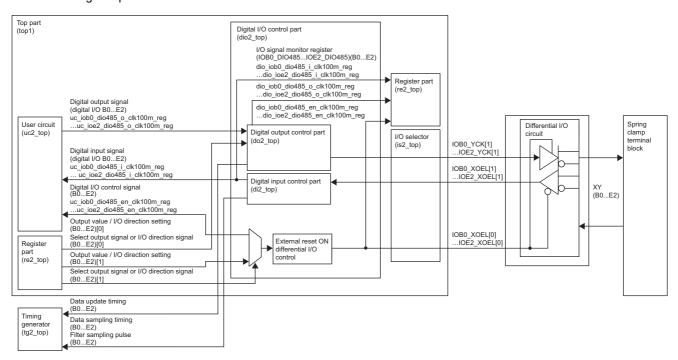

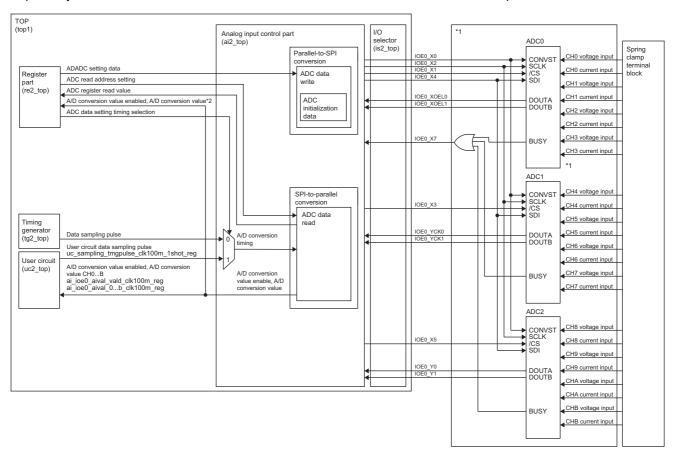

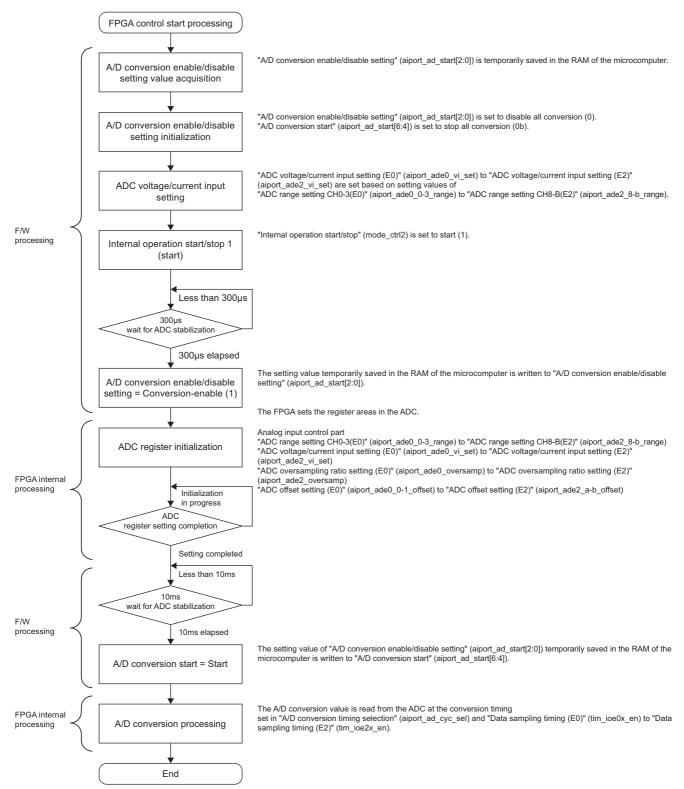

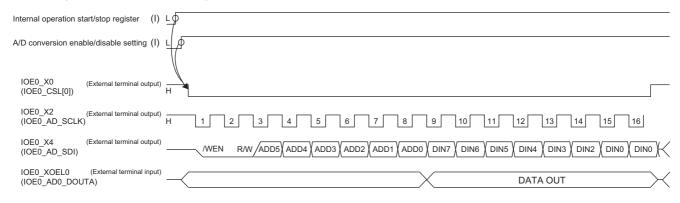

|      | FPGA peripheral circuit structure                                     |     |

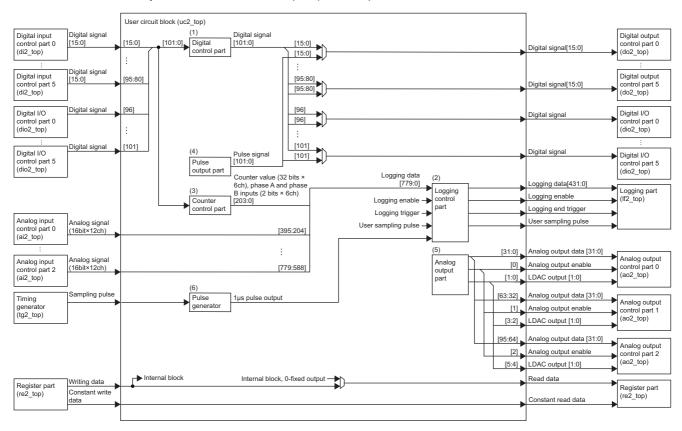

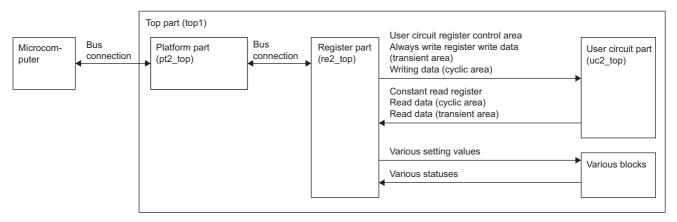

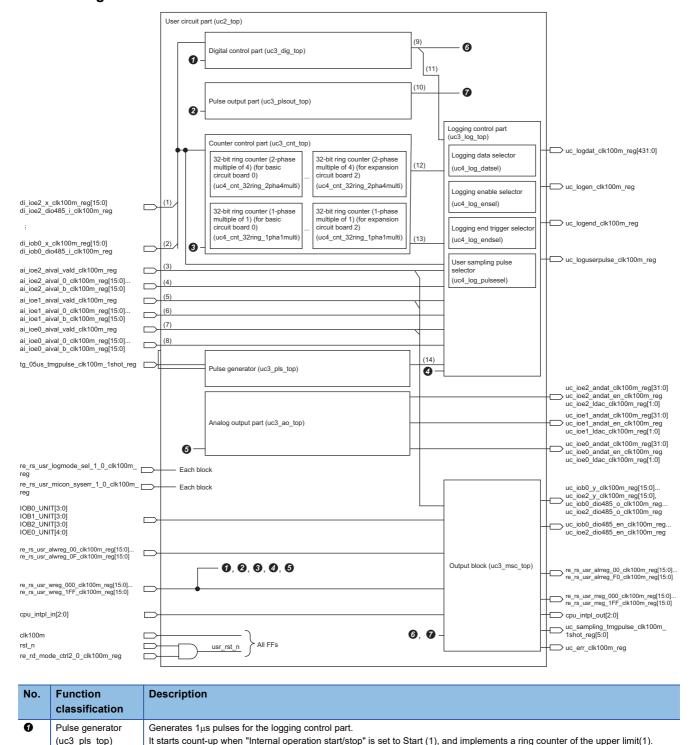

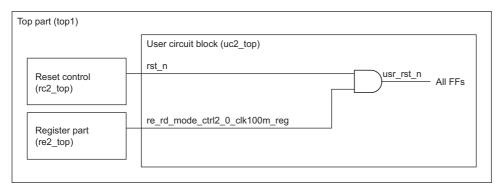

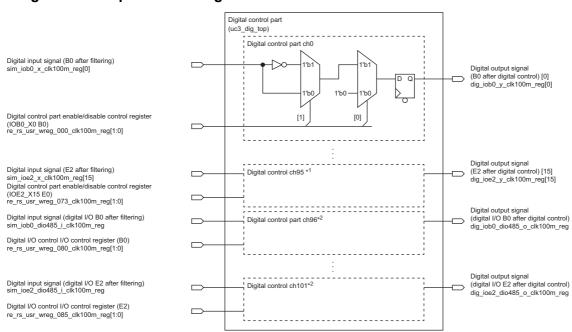

|      | Function blocks                                                       | 182 |

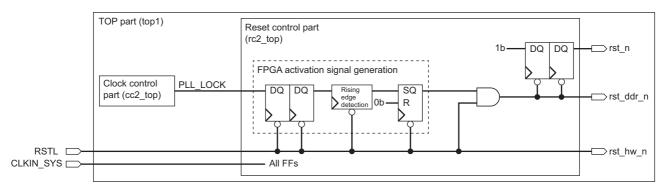

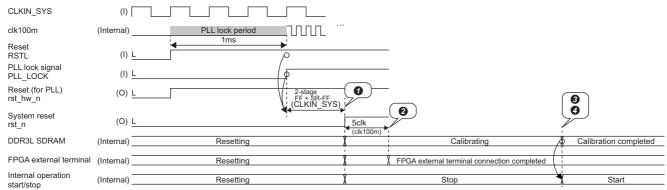

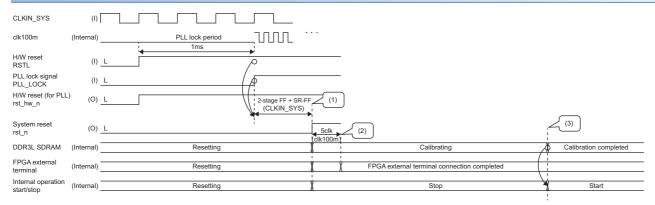

|      | Reset system diagram                                                  |     |

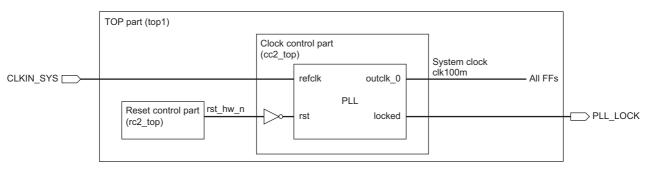

|      | Clock system diagram                                                  | 186 |

|      | FPGA external terminal list                                           | 186 |

|      | FPGA memory map                                                       | 186 |

|      | Register                                                              |     |

| 11.2 | Details                                                               |     |

| 11.3 | Standard Circuit                                                      |     |

|      | Module common circuit                                                 |     |

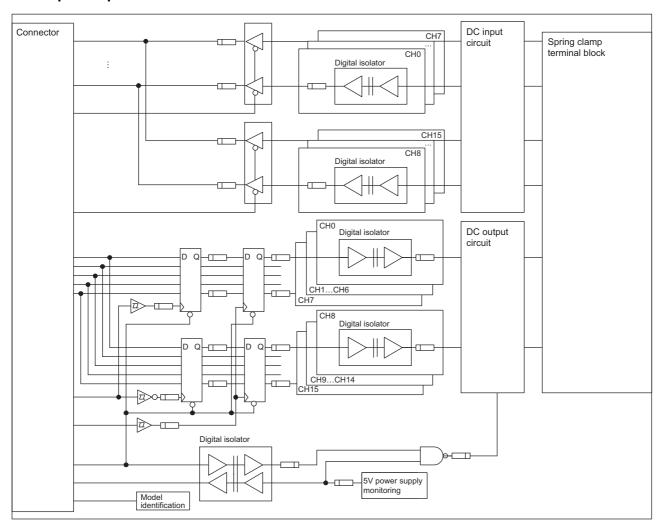

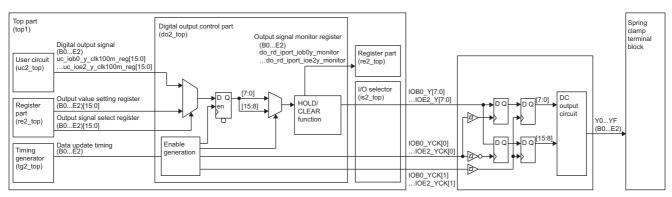

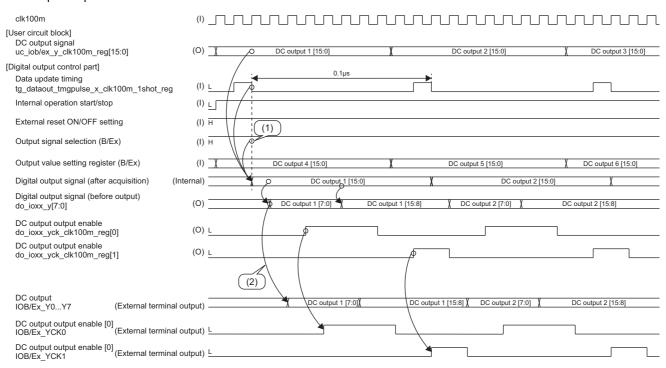

|      | Module specific circuit (NZ2GN2S-D41P01)                              |     |

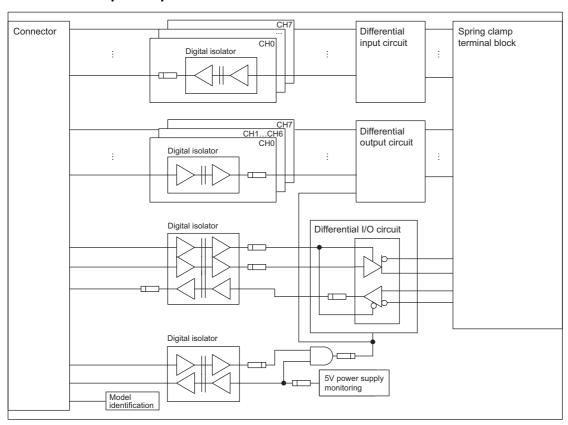

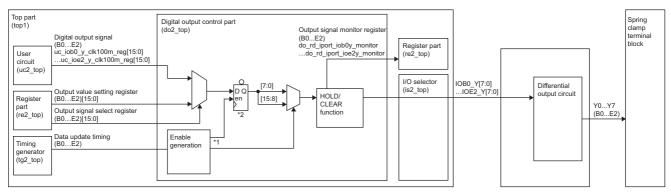

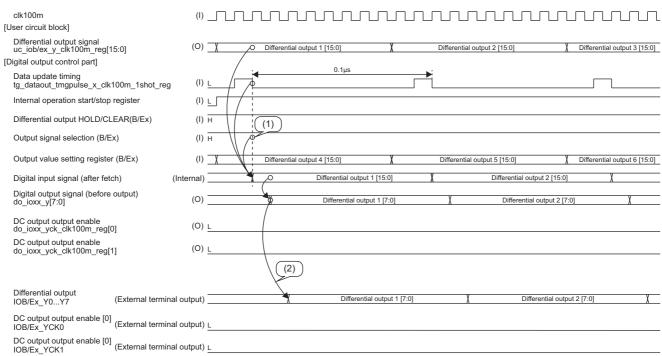

|      | Module specific circuit (NZ2GN2S-D41D01)                              |     |

|      | Module specific circuit (NZ2GN2S-D41PD02)                             |     |

|      | Module specific circuit (NZ2EX2S-D41P01)                              |     |

|      | Module specific circuit (NZ2EX2S-D41D01)                              |     |

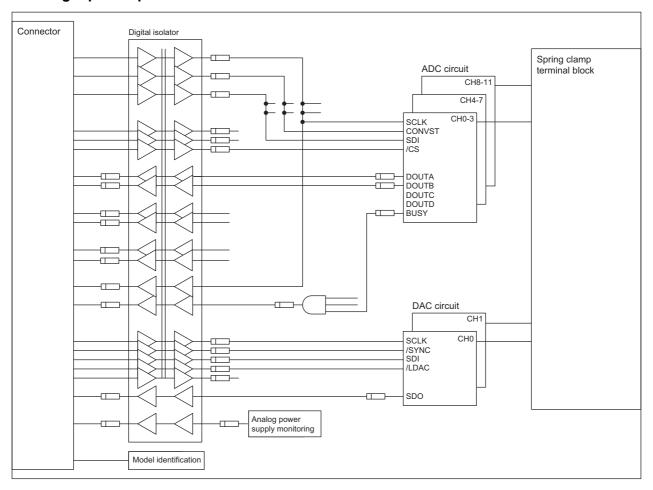

|      | Module specific circuit (NZ2EX2S-D41A01)                              |     |

|      | Notes and restrictions                                                |     |

| 11.4 | User Circuit Block                                                    |     |

|      | Module common interface                                               |     |

|      | NZ2GN2S-D41P01, NZ2GN2S-D41PD02, NZ2EX2S-D41P01                       |     |

|      | NZ2GN2S-D41D01, NZ2GN2S-D41PD02, NZ2EX2S-D41D01                       |     |

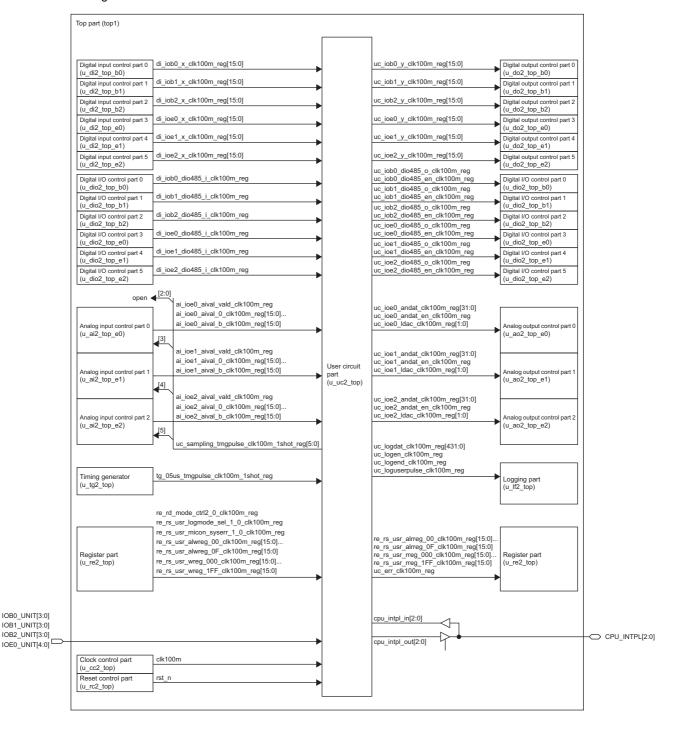

|      | NZ2EX2S-D41A01                                                        |     |

|      | IF specification notes/restrictions                                   |     |

|      | Sample circuit                                                        |     |

|      | Cample on suk                                                         |     |

| PA   | RT 6 FUNCTIONS                                                        |     |

| CILA | DTED 42 EUNCTIONS                                                     | 000 |

|      | APTER 12 FUNCTIONS                                                    | 298 |

| 12.1 | Function List  Operation Mode Shift at Power-On                       |     |

| 12.2 |                                                                       |     |

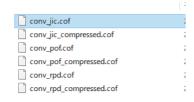

| 12.3 | FPGA Download Function                                                |     |

|      | How to write via JTAG                                                 |     |

|      | How to write via Ethernet.                                            |     |

| 40.4 | Procedure for conversion from SOF format to JIC format and RPD format |     |

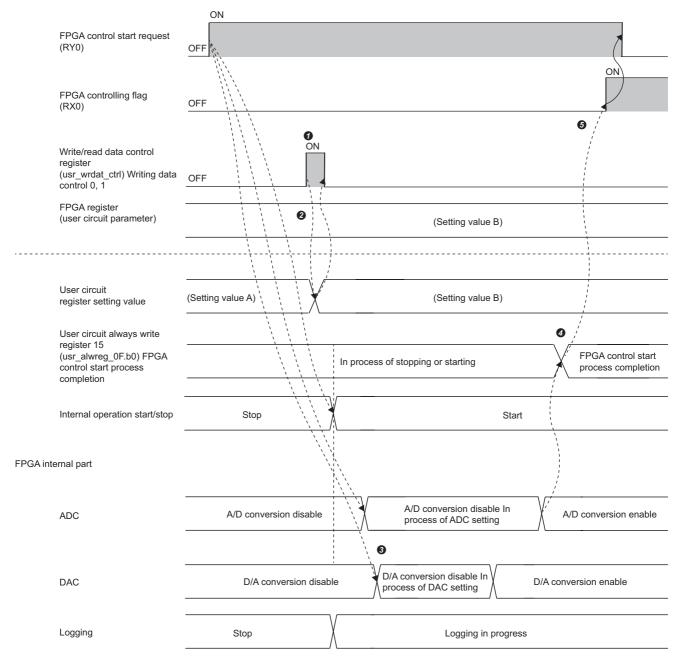

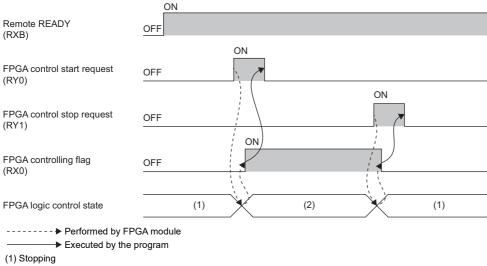

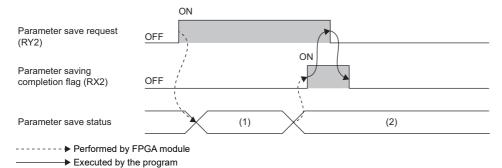

| 12.4 | FPGA Configuration Function  FPGA Control Function                    |     |

| 12.5 |                                                                       |     |

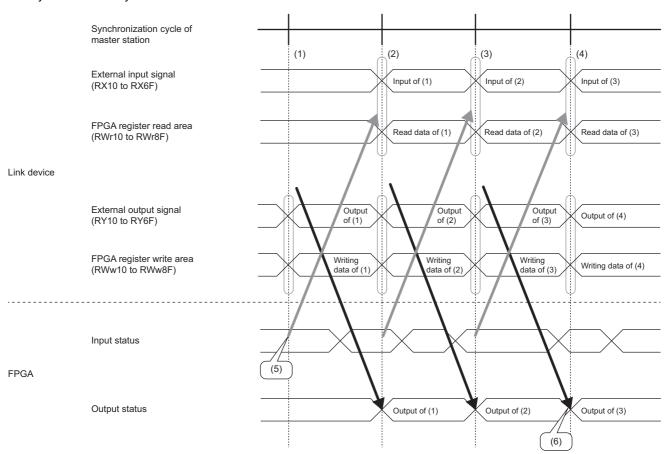

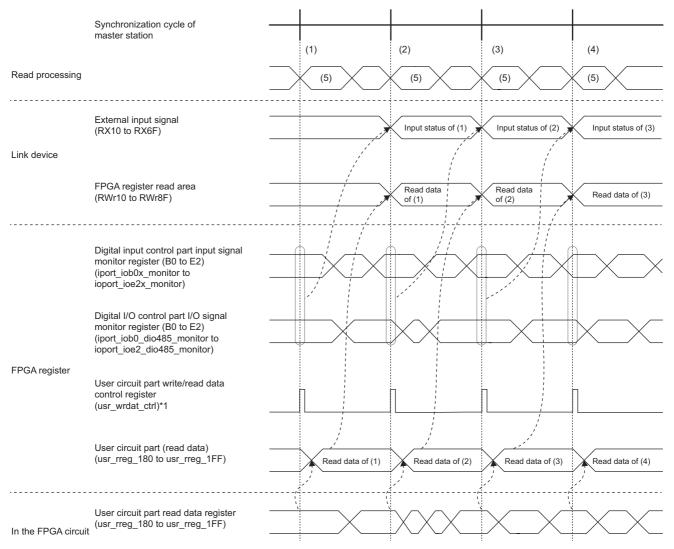

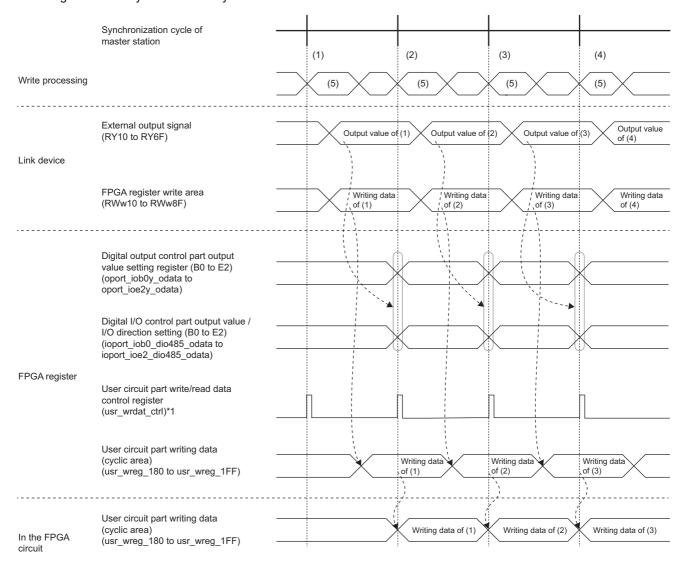

| 12.6 | FPGA Register Access Function                                         |     |

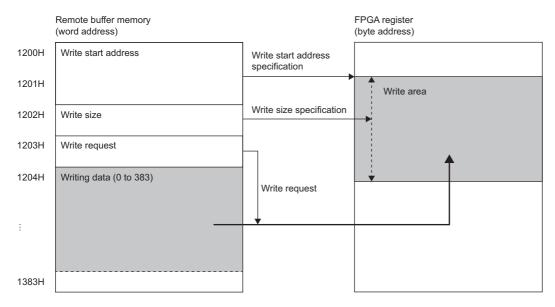

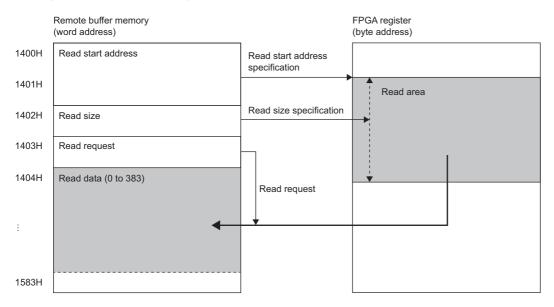

|        | Remote register method                                                                 | 321        |

|--------|----------------------------------------------------------------------------------------|------------|

|        | Method using remote buffer memory                                                      | 324        |

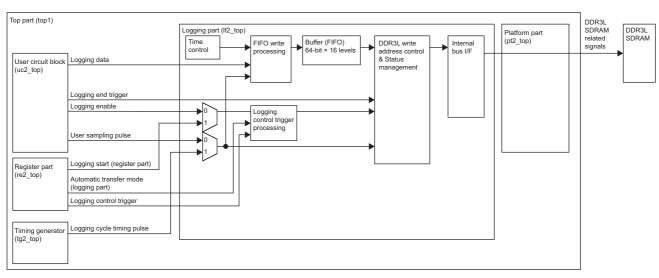

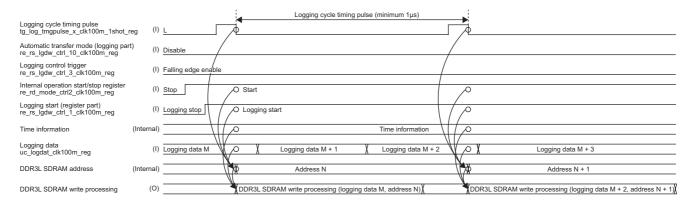

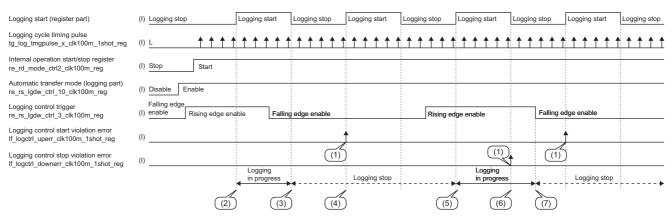

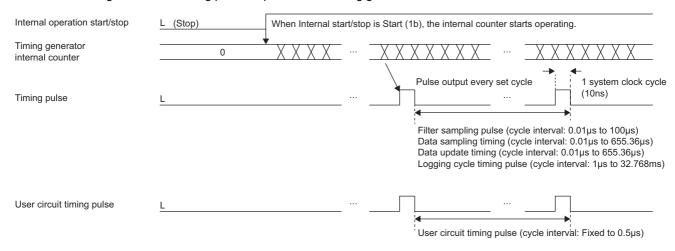

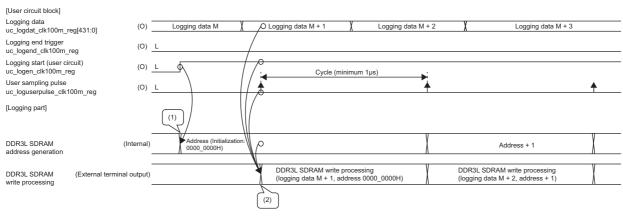

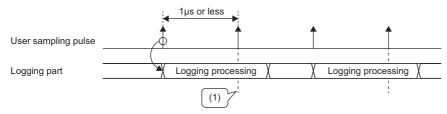

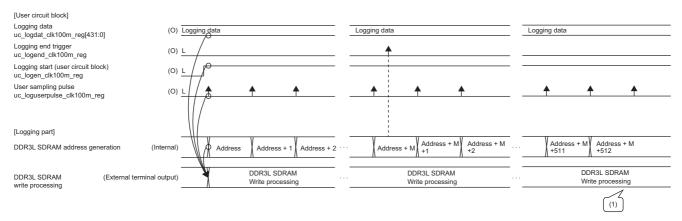

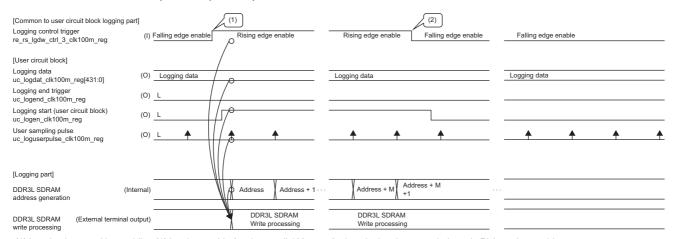

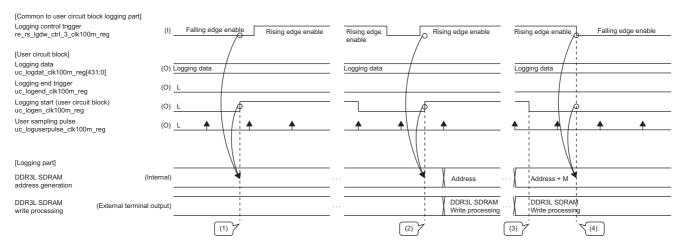

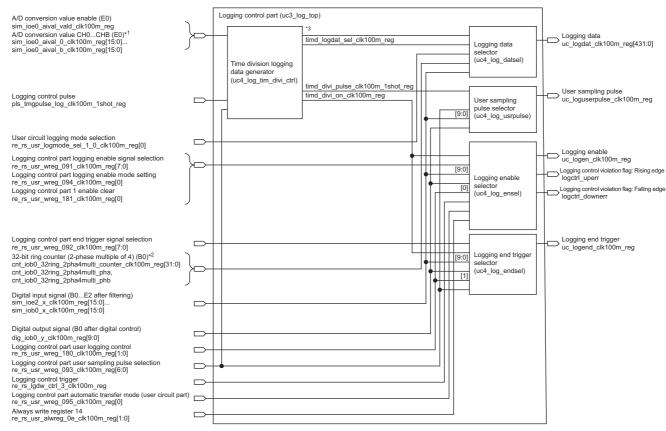

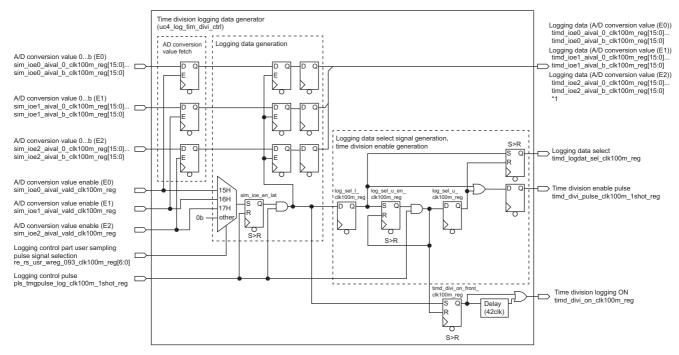

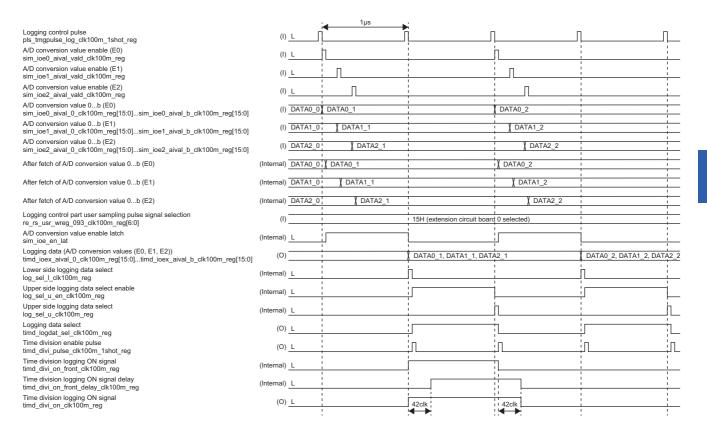

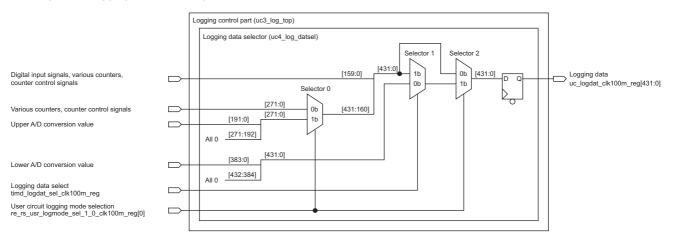

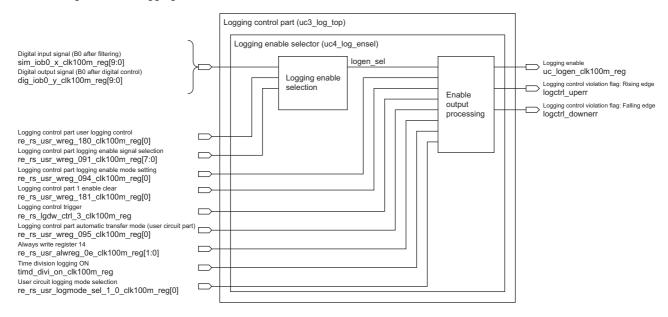

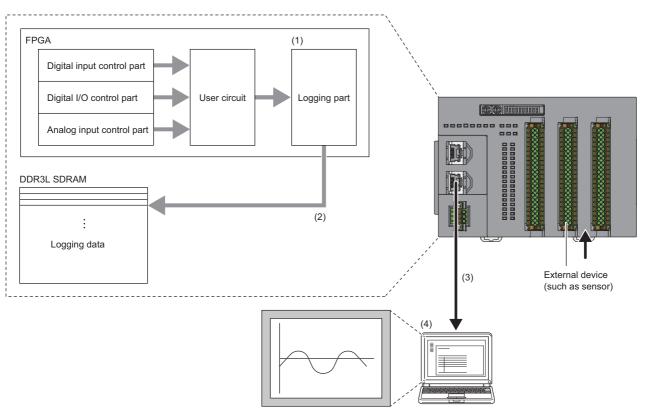

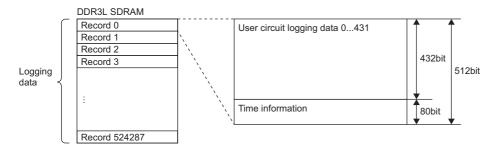

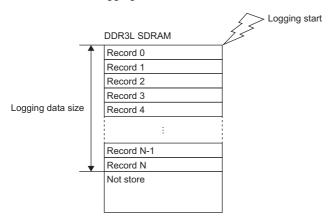

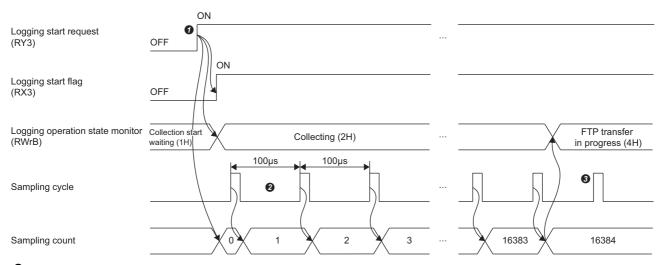

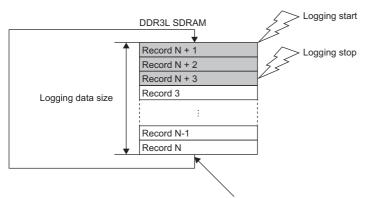

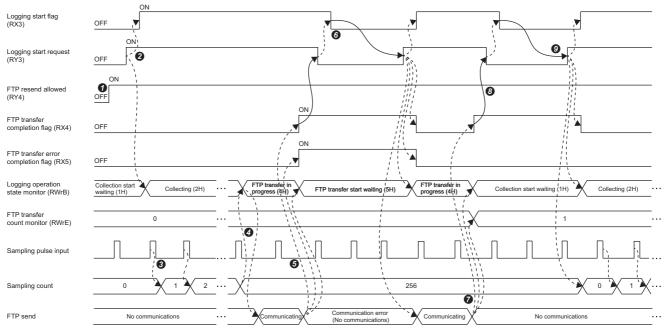

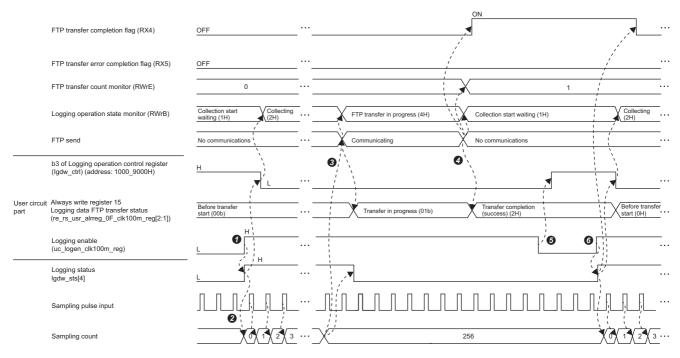

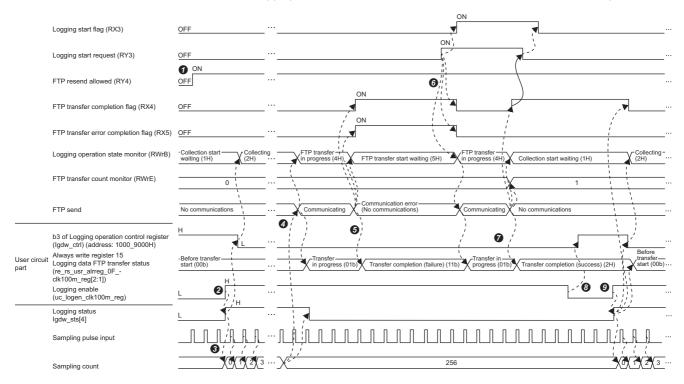

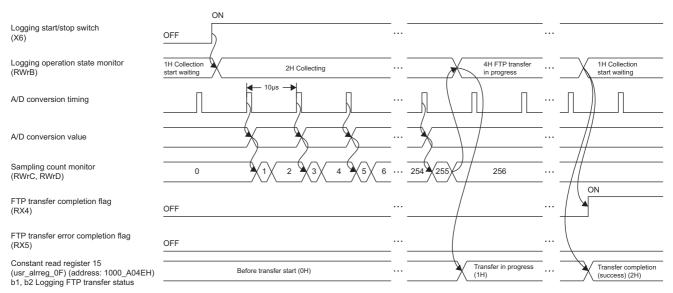

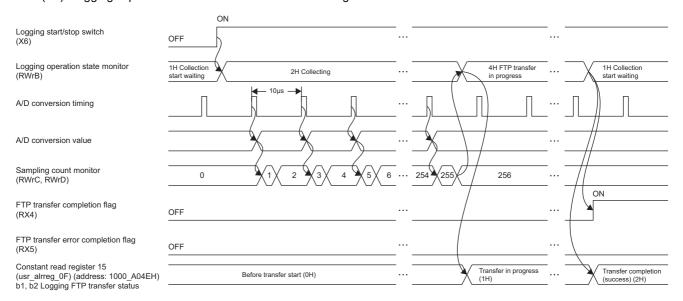

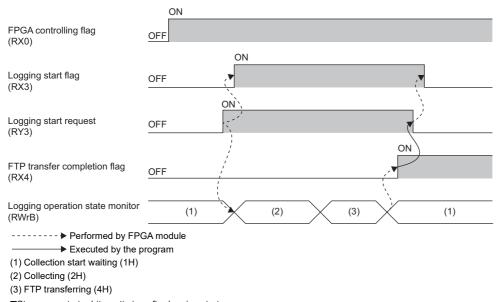

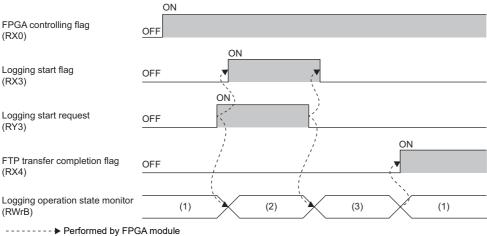

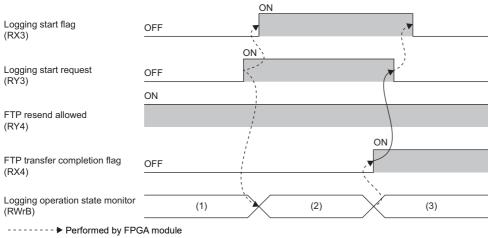

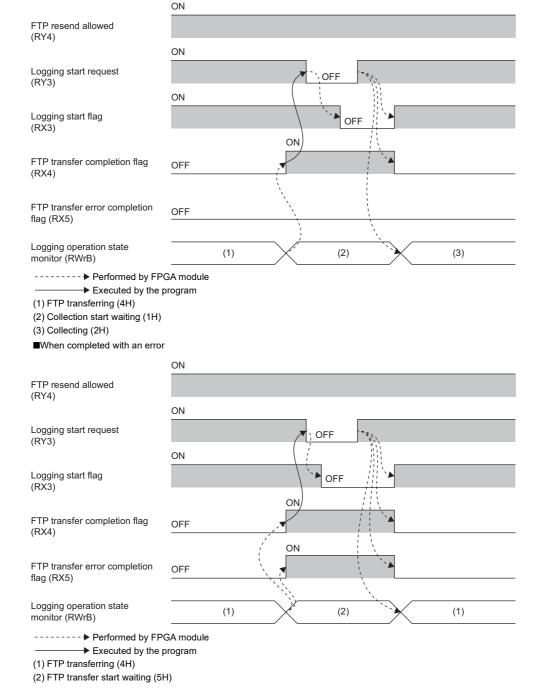

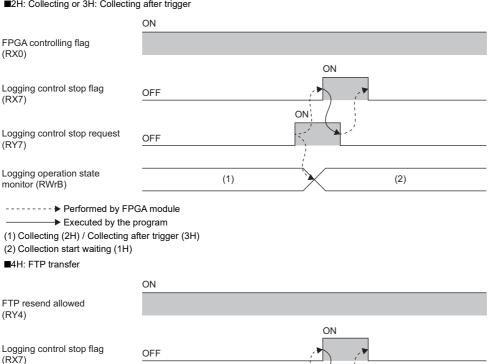

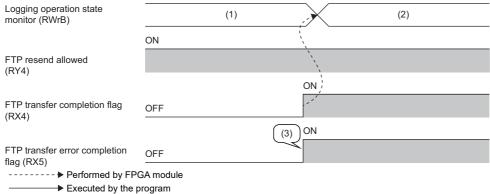

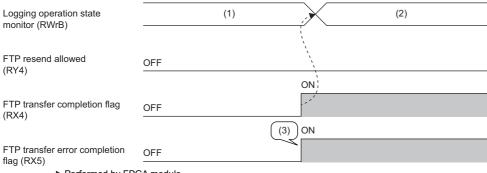

| 12.7   | Logging Function                                                                       | 327        |

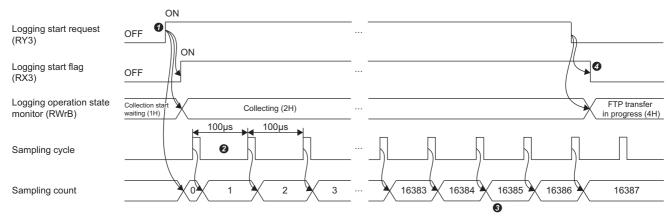

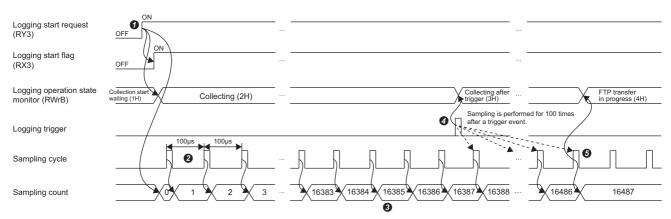

|        | Logging control                                                                        | 328        |

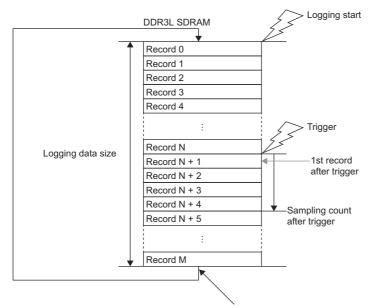

|        | Record details                                                                         | 331        |

|        | Time setting                                                                           | 332        |

|        | Operation example                                                                      | 333        |

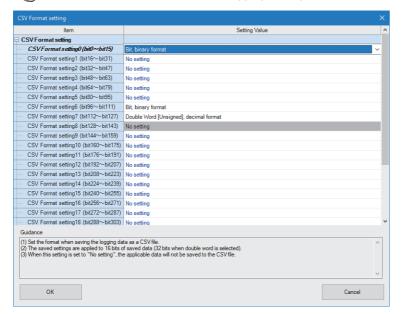

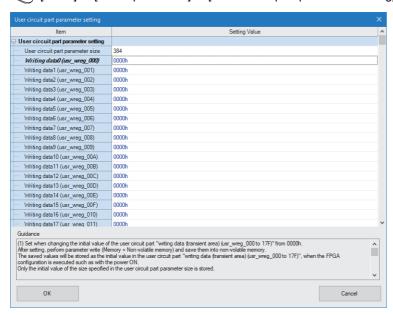

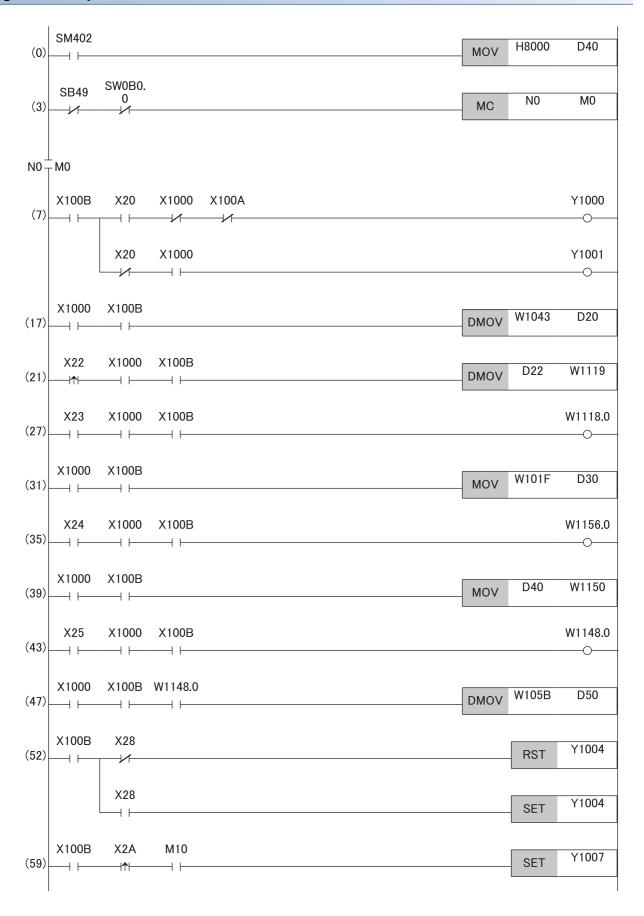

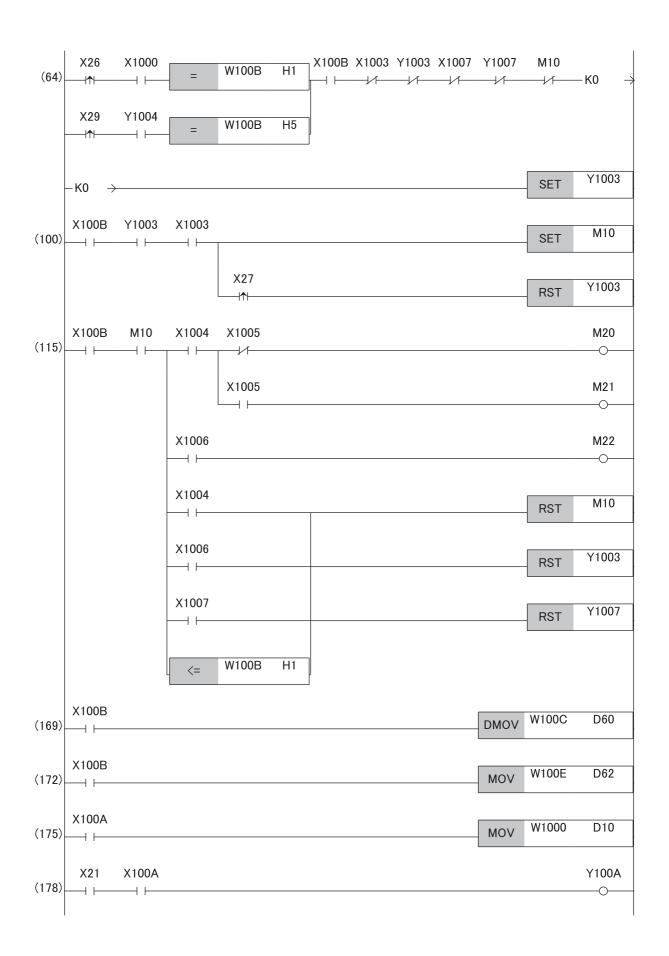

|        | Setting method                                                                         | 337        |

|        | Logging monitor                                                                        |            |

|        | Precautions                                                                            |            |

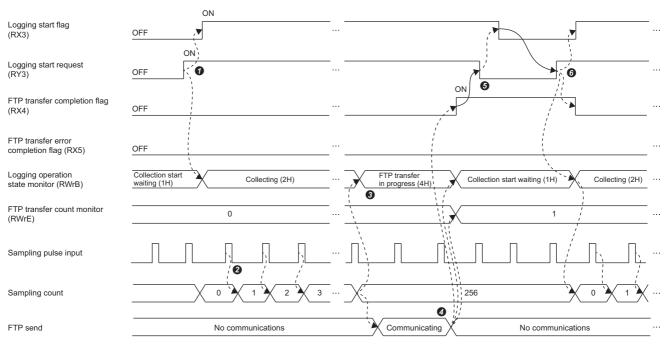

| 12.8   | FTP Client Function.                                                                   |            |

|        | File saving format of logging data                                                     |            |

|        | Operation example                                                                      |            |

|        | Precautions                                                                            |            |

| 12.9   | SLMP Communication Function                                                            |            |

| 12.5   |                                                                                        |            |

|        | •                                                                                      |            |

| 12.11  | Module Power Supply Voltage Drop Detection Function                                    |            |

| 12.12  | Firmware Update Function                                                               | 361        |

|        |                                                                                        |            |

| PA     | RT 7 SAMPLE CIRCUIT                                                                    |            |

|        |                                                                                        |            |

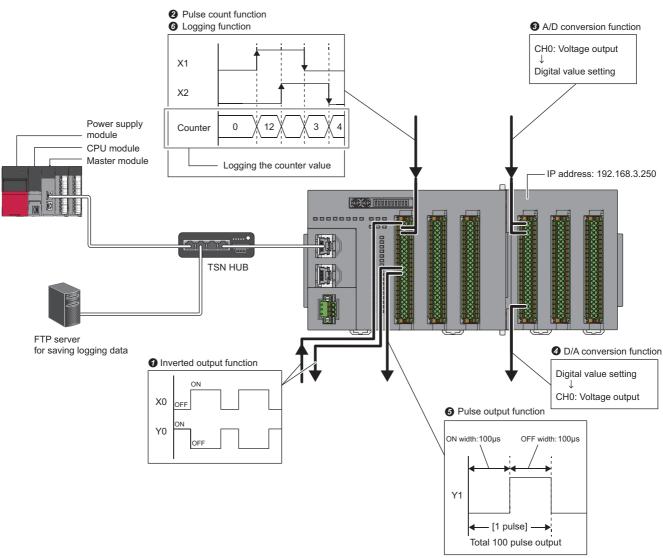

| СНД    | PTER 13 SAMPLE CIRCUIT IN STANDALONE MODE                                              | 366        |

|        |                                                                                        |            |

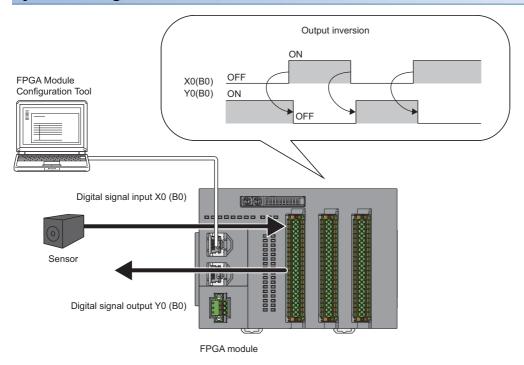

| 13.1   | When Using the Inversion Output Function                                               |            |

| 13.2   | When Using the Pulse Count Function                                                    |            |

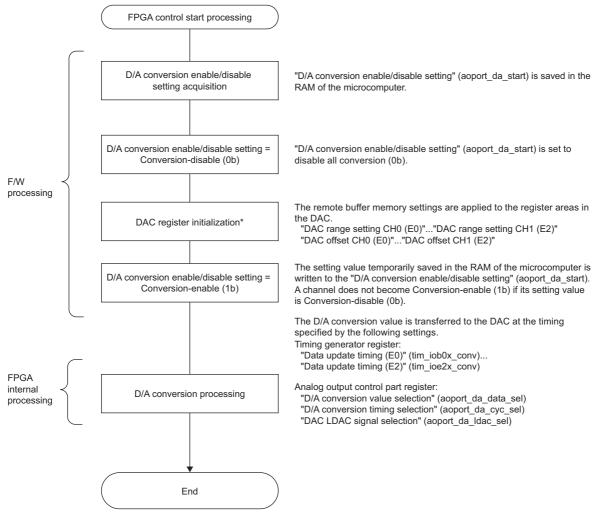

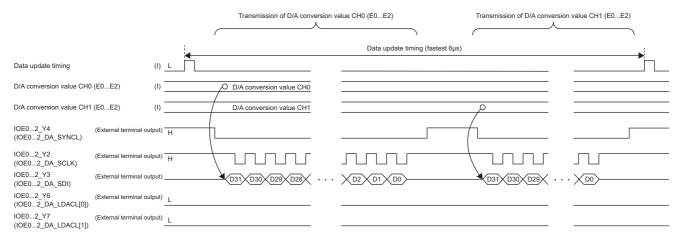

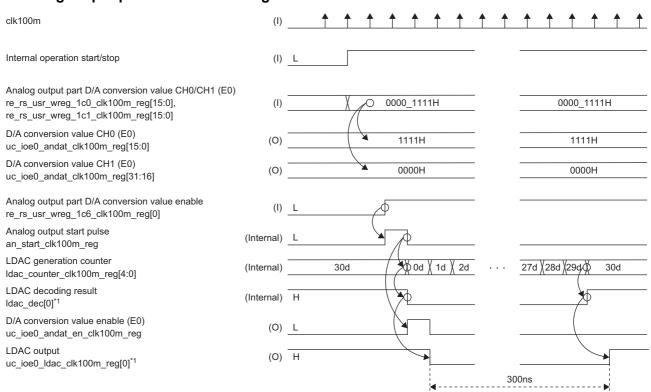

| 13.3   | When Using the D/A Conversion Function                                                 |            |

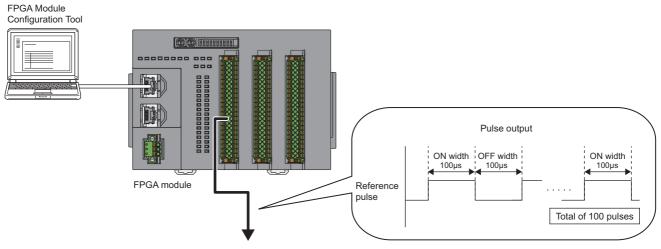

| 13.4   | When Using the Pulse Output Function                                                   |            |

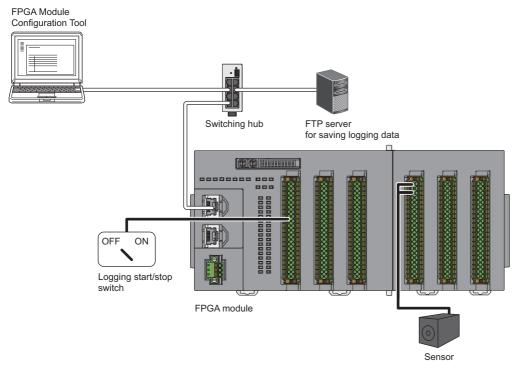

| 13.5   | When Using the Logging Function                                                        | 384        |

|        | Logging external inputs and counters                                                   | 384        |

|        | Logging A/D conversion values                                                          | 390        |

|        |                                                                                        |            |

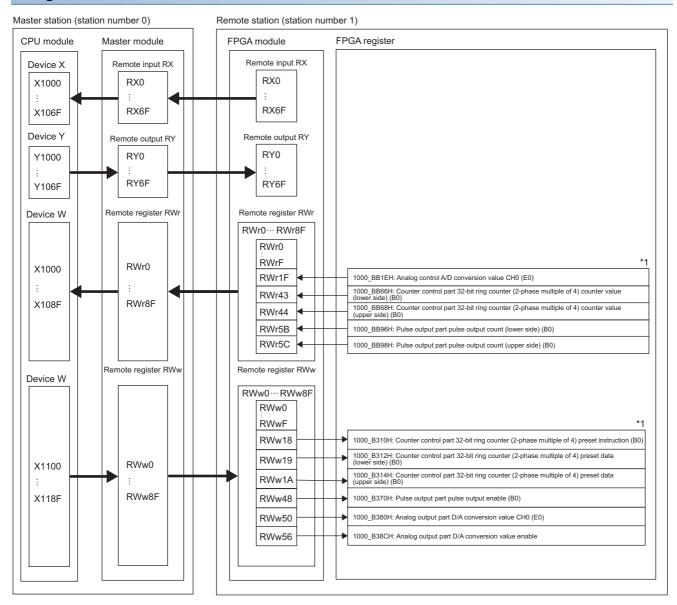

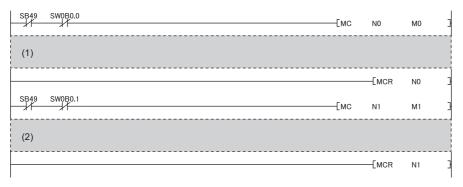

| СНА    | PTER 14 SAMPLE CIRCUIT IN CC-LINK IE TSN COMMUNICATION MODE                            | 396        |

| 14.1   | Precautions for Programming                                                            | 401        |

| 14.2   | When Using the Inversion Output Function                                               | 402        |

| 14.3   | When Using the Pulse Count Function                                                    | 405        |

| 14.4   | When Using the A/D Conversion Function                                                 |            |

| 14.5   | When Using the D/A Conversion Function                                                 |            |

| 14.6   | When Using the Pulse Output Function                                                   |            |

| 14.7   | When Using the Logging Function                                                        |            |

| 14.8   | Program Examples                                                                       |            |

| 14.0   | 1 Togram Examples                                                                      | 741        |

|        |                                                                                        |            |

| $\Box$ | DT 0 TROUBLESHOOTING                                                                   |            |

| PA     | RT 8 TROUBLESHOOTING                                                                   |            |

| PA     | RT 8 TROUBLESHOOTING                                                                   |            |

|        | RT 8 TROUBLESHOOTING  PTER 15 MAINTENANCE AND INSPECTION                               | 428        |

|        |                                                                                        | 428        |

| СНА    |                                                                                        | 428<br>430 |

| СНА    | PTER 15 MAINTENANCE AND INSPECTION                                                     |            |

| CHA    | PTER 15 MAINTENANCE AND INSPECTION                                                     | 430        |

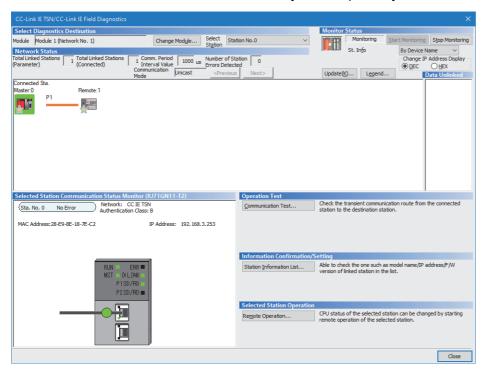

| CHA    | PTER 15 MAINTENANCE AND INSPECTION PTER 16 CC-Link IE TSN/CC-Link IE Field DIAGNOSTICS | 430        |

| CHAPTER 18 CHECKING THE LEDS                             | 434 |

|----------------------------------------------------------|-----|

| CHAPTER 19 UNIT TEST                                     | 438 |

| CHAPTER 20 TROUBLESHOOTING BY SYMPTOM                    | 440 |

| CHAPTER 21 TROUBLESHOOTING DURING FPGA DEVELOPMENT       | 443 |

| CHAPTER 22 TROUBLE EXAMPLES of DC INPUT/OUTPUT           | 445 |

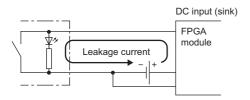

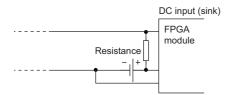

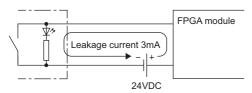

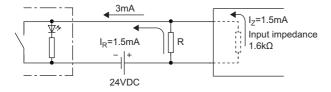

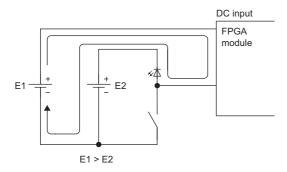

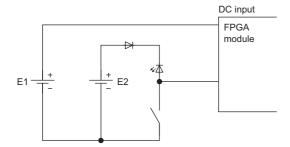

| 22.1 Troubles and Countermeasures for DC Input Circuits  | 445 |

| 22.2 Troubles and Countermeasures for DC Output Circuits | 448 |

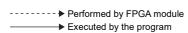

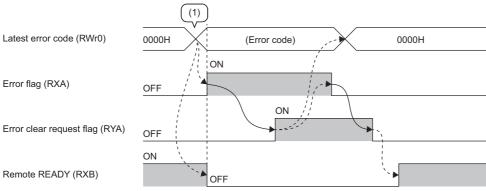

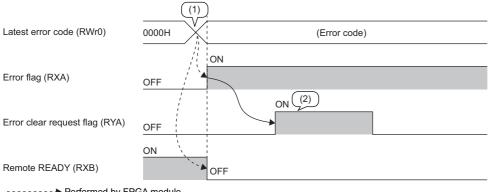

| CHAPTER 23 CHECK/CLEAR ERROR CODES                       | 450 |

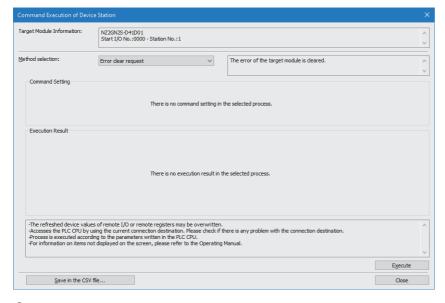

| 23.1 Checking Error Codes                                | 450 |

| 23.2 Clearing Error Codes                                | 452 |

| CHAPTER 24 ERROR CODE LIST                               | 453 |

| APPENDICES                                               | 463 |

| Appendix 1 Remote I/O Signal                             | 463 |

| List of remote I/O signals                               | 463 |

| Details of remote input signals                          | 469 |

| Details of remote output signals                         |     |

| Appendix 2 Remote Register                               |     |

| List of remote registers                                 |     |

| Details of remote registers                              |     |

| Appendix 3 Remote Buffer Memory                          |     |

| List of remote buffer memory areas                       |     |

| Details of remote buffer memory                          |     |

| Appendix 4 FPGA register                                 |     |

| List of FPGA register areas                              |     |

| FPGA register details (reset control part)               |     |

| FPGA register details (timing generator)                 |     |

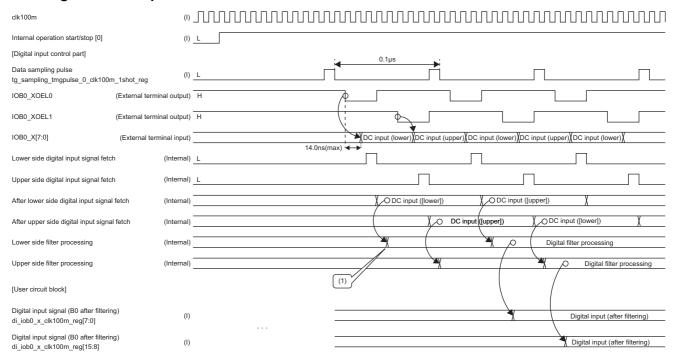

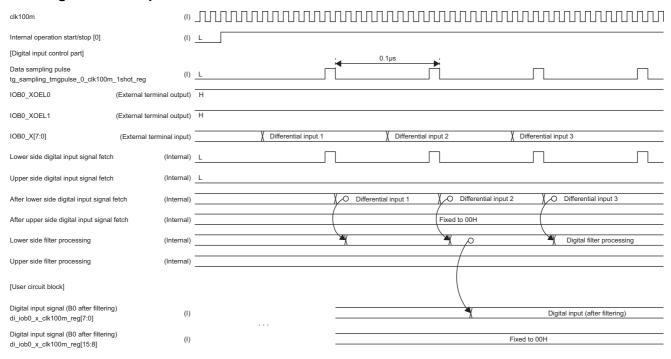

| FPGA register details (digital input control part)       |     |

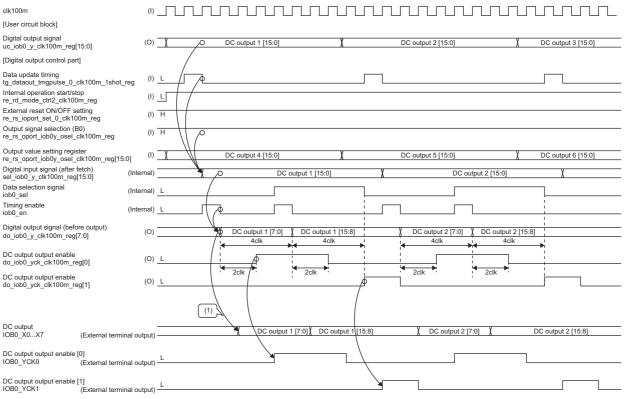

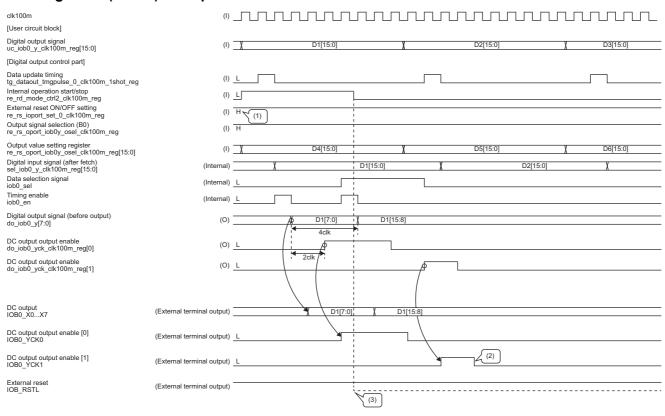

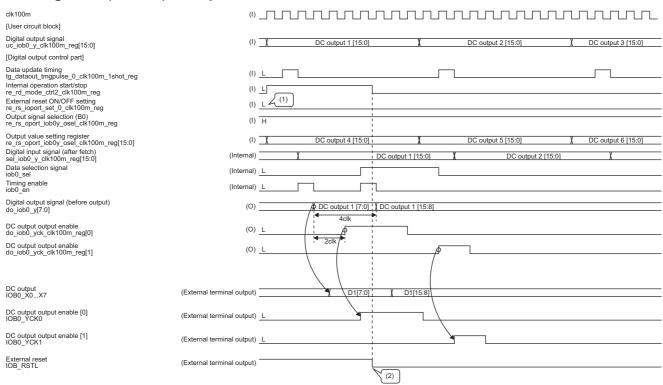

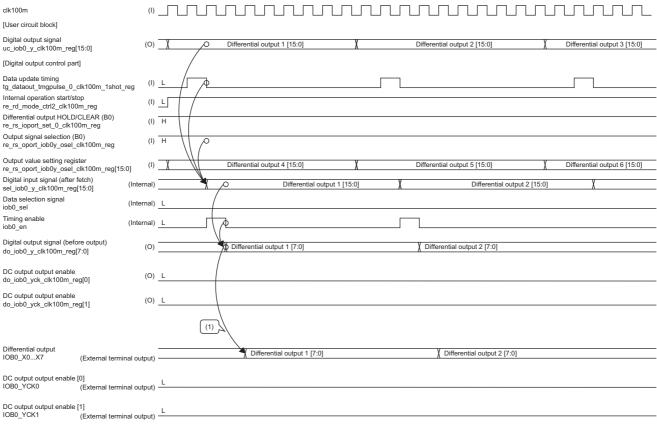

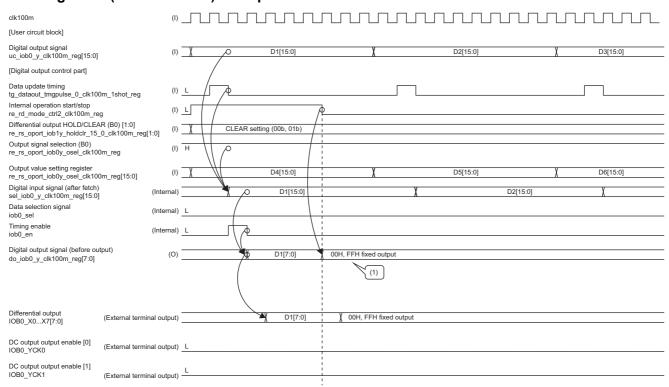

| FPGA register details (digital output control part)      |     |

| FPGA register details (digital I/O control part)         |     |

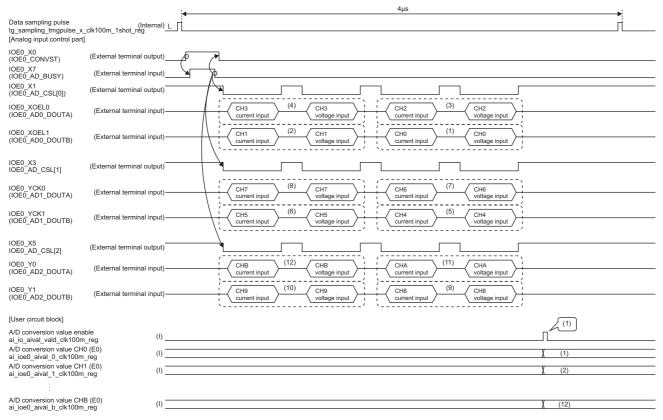

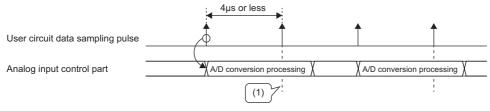

| FPGA register details (analog input control part).       |     |

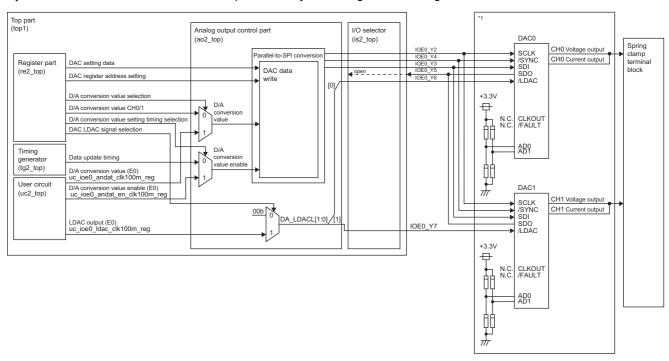

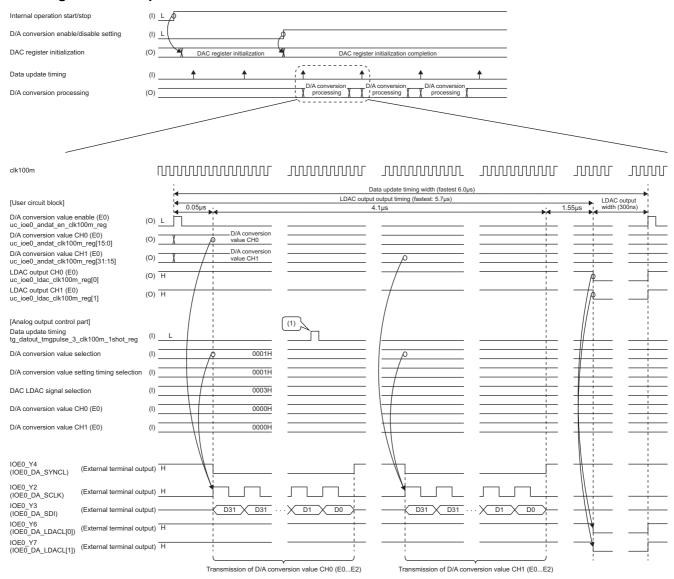

| FPGA register details (analog output control part)       |     |

| FPGA register details (logging part)                     |     |

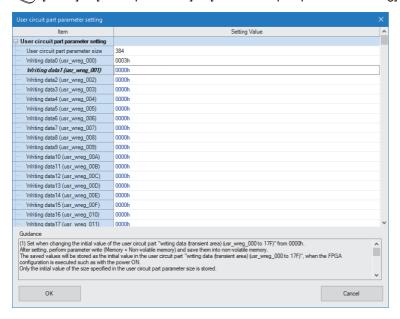

| FPGA register details (user circuit)                     |     |

| FPGA register details (sample circuit register)          |     |

| Appendix 6 A List of FPGA External Terminals             |     |

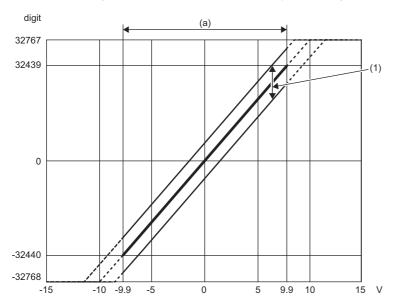

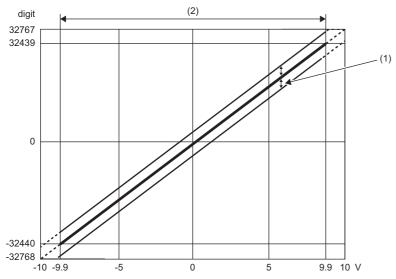

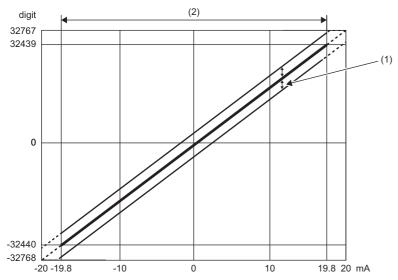

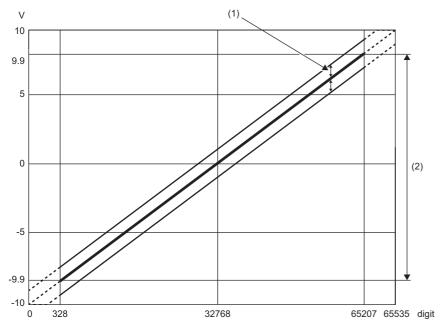

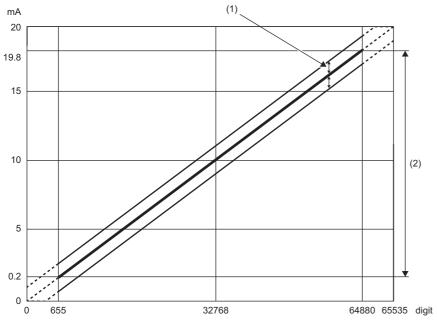

| Appendix 7 I/O Conversion Characteristics and Accuracy   |     |

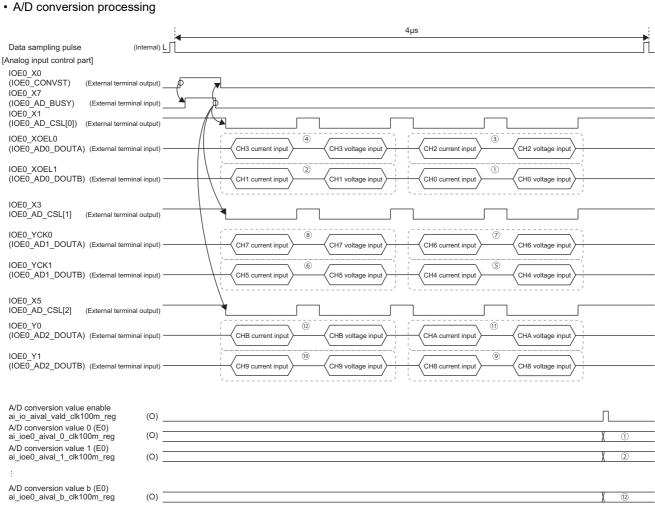

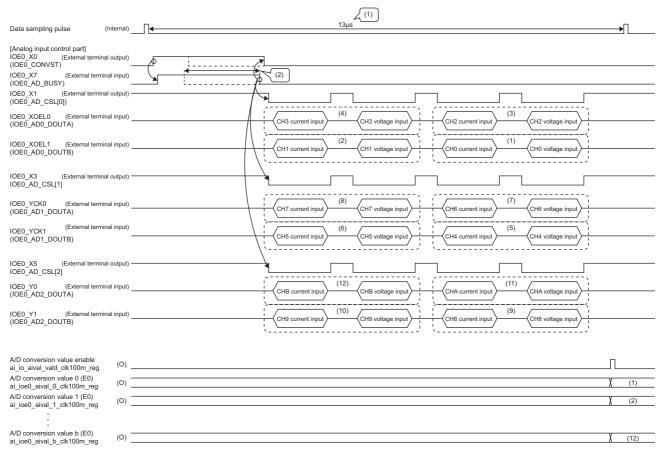

| A/D conversion                                           |     |

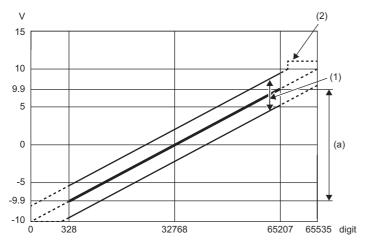

| D/A conversion                                           |     |

| Appendix 8 CC-Link IE TSN Processing Time                |     |

| Appendix 9 Logging Data FTP Transfer Time                |     |

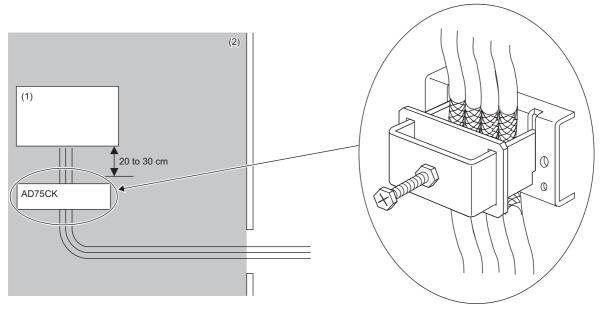

| Appendix 10 EMC and Low Voltage Directives               |     |

| Measures to comply with the EMC Directive                |     |

| Requirements for compliance with the Low Voltage Directive           |     |

|----------------------------------------------------------------------|-----|

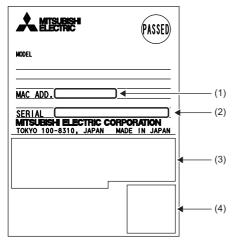

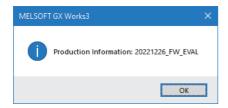

| Appendix 11 How to Check Production Information and Firmware Version | 690 |

| Checking the production information                                  | 690 |

| Checking the firmware version                                        | 691 |

| Appendix 12 Port Number                                              | 692 |

| Appendix 13 Warning List                                             | 693 |

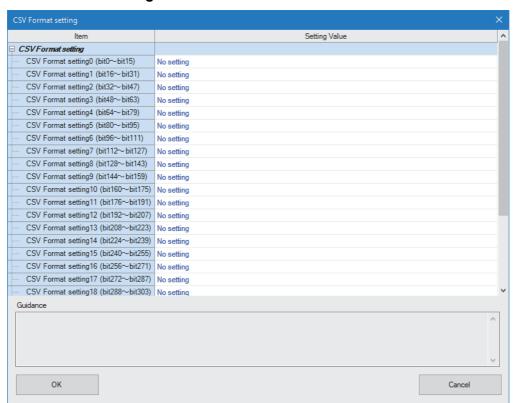

| Appendix 14 Logging Data Bit Assignment                              | 714 |

| Appendix 15 Open Source Software License                             | 742 |

| Appendix 16 Support                                                  |     |

| Technical support assistance service regarding FPGA module           |     |

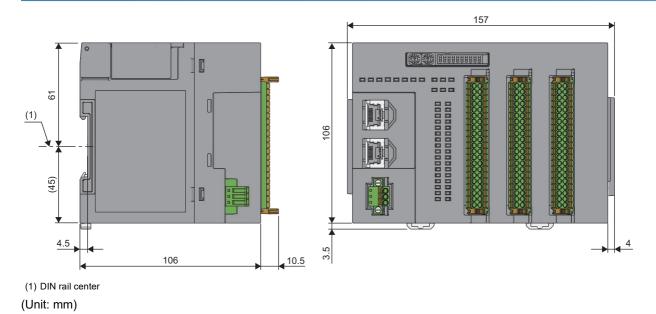

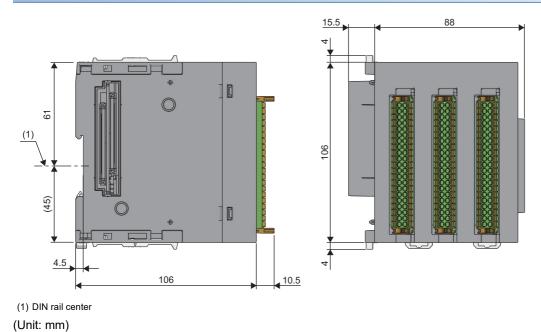

| Appendix 17 External Dimensions                                      | 746 |

| INDEX                                                                | 748 |

| REVISIONS                                                            | 750 |

| WARRANTY                                                             |     |

| TRADEMARKS                                                           |     |

| COPYRIGHTS                                                           | 752 |

## **RELEVANT MANUALS**

For the latest e-Manual and manual PDF, please consult your local Mitsubishi representative.

| Manual name [manual number]              | Description                                                                                                                                                                         | Available form  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| CC-Link IE TSN FPGA Module User's Manual | Part names, specifications, procedures before operation, system configuration,                                                                                                      | Print book      |

| [SH-082569ENG] (this manual)             | installation, wiring, settings, FPGAs, functions, sample circuits, troubleshooting, remote I/O signals, remote register, remote buffer memory, and FPGA register of the FPGA module | e-Manual<br>PDF |

e-Manual refers to the Mitsubishi Electric FA electronic book manuals that can be browsed using a dedicated tool.

e-Manual has the following features:

- Required information can be cross-searched in multiple manuals.

- Other manuals can be accessed from the links in the manual.

- The hardware specifications of each part can be found from the product figures.

- Pages that users often browse can be bookmarked.

- Sample programs can be copied to an engineering tool.

## **TERMS**

Unless otherwise specified, this manual uses the following terms.

| Term                                                            | Description                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

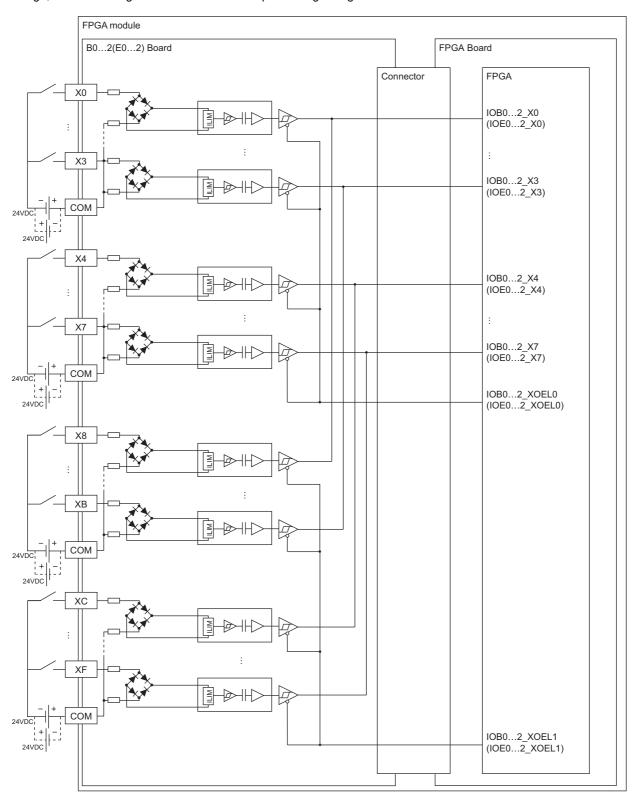

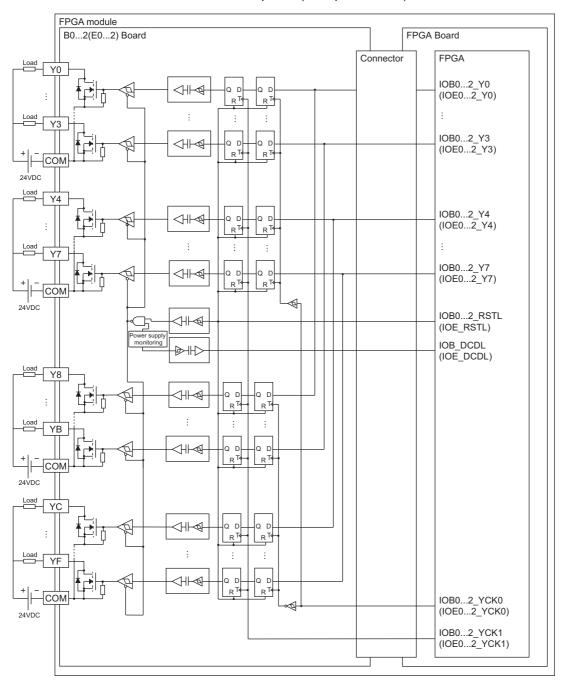

| B0 to B2                                                        | A terminal block or a circuit board of B0 to B2 for the main module                                                                                                                                                                                                                                                       |

| CC-Link IE TSN Class*1                                          | A group of devices and switching hubs compatible with CC-Link IE TSN, ranked according to the functions and performance by the CC-Link Partner Association.  For CC-Link IE TSN Class, refer to the CC-Link IE TSN Installation Manual (BAP-C3007ENG-001) published by the CC-Link Partner Association.                   |

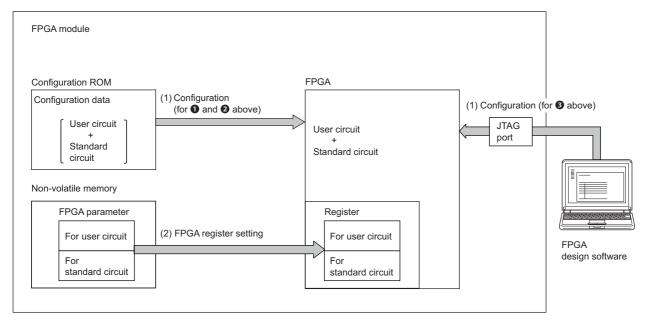

| Configuration                                                   | Operation of writing configuration data to the FPGA                                                                                                                                                                                                                                                                       |

| Configuration data                                              | Information of the FPGA circuits                                                                                                                                                                                                                                                                                          |

| Configuration ROM                                               | A non-volatile memory that stores configuration data                                                                                                                                                                                                                                                                      |

| Cyclic transmission                                             | A function by which data are periodically exchanged among stations on the same network using link devices                                                                                                                                                                                                                 |

| Data link                                                       | Communications performed by cyclic transmission and transient transmission                                                                                                                                                                                                                                                |

| Dedicated instruction                                           | An instruction that simplifies programming for using functions of intelligent function modules                                                                                                                                                                                                                            |

| Device station                                                  | A station other than a master station: a local station, a remote station                                                                                                                                                                                                                                                  |

| E0 to E2                                                        | A terminal block or a circuit board of E0 to E2 for the extension module                                                                                                                                                                                                                                                  |

| Engineering tool                                                | A tool used for setting up programmable controllers, programming, debugging, and maintenance                                                                                                                                                                                                                              |

| Extension module                                                | An FPGA module that cannot be used alone. The number of I/O points can be increased or analog I/O can be added by connecting an extension module to the main module.                                                                                                                                                      |

| FPGA development environment for the CC-Link IE TSN FPGA module | A set of data such as design environment (RTL), verification environment, and logic synthesis environment for the FPGA module                                                                                                                                                                                             |

| FPGA development software                                       | Development software used for FPGA circuit design. Another name for Intel® Quartus Prime.                                                                                                                                                                                                                                 |

| FPGA download                                                   | Operation of writing configuration data to the FPGA or the configuration ROM                                                                                                                                                                                                                                              |

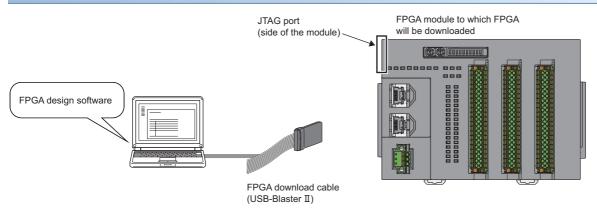

| FPGA download cable                                             | A cable to connect the JTAG connector of the FPGA module to the personal computer. Access to the FPGA module from the personal computer is possible by using FPGA development software. The FPGA download cable is another name for Intel <sup>®</sup> FPGA Download Cable II (former name: USB-Blaster <sup>™</sup> II). |

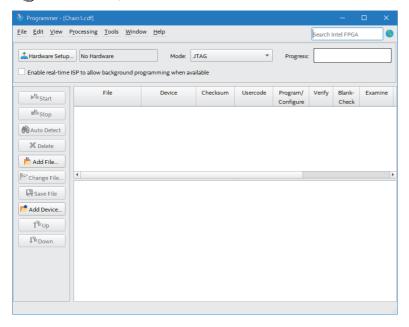

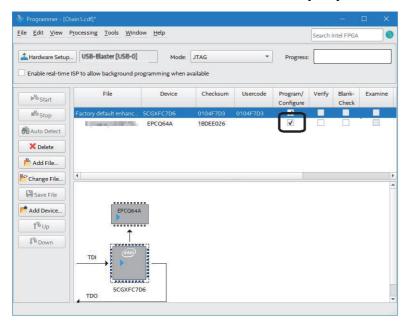

| FPGA Module Configuration Tool                                  | A tool to set the parameters of the FPGA module or perform the FPGA download                                                                                                                                                                                                                                              |

| FPGA parameter                                                  | A parameter to change the operation of the FPGA                                                                                                                                                                                                                                                                           |

| FPGA register                                                   | A register for the standard circuits and the user circuit                                                                                                                                                                                                                                                                 |

| General-purpose hub                                             | A CC-Link IE TSN Class A switching hub authorized by CC-Link Partner Association                                                                                                                                                                                                                                          |

| Link device                                                     | A device (RX, RY, RWr, or RWw) in an FPGA module                                                                                                                                                                                                                                                                          |

| Link scan (link scan time)                                      | Time required for all the stations on the network to transmit data.  The link scan time depends on data volume and the number of transient transmission requests.                                                                                                                                                         |

| Local station                                                   | A station that performs cyclic transmission and transient transmission with the master station and other local stations                                                                                                                                                                                                   |

| Term                   | Description                                                                                                                                                                                                                                                                                    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main module            | An FPGA module with the communication function. The main module can be used alone. One extension module can be connected to a main module.                                                                                                                                                     |

| Master station         | A station that controls the entire network. This station can perform cyclic transmission and transient transmission with all stations.  Only one master station can be used in a network.                                                                                                      |

| Module parameter       | Parameters to set the FPGA module functions except the FPGA operation                                                                                                                                                                                                                          |

| Multicast filter       | A filter function that selects whether to send cyclic data of multicast mode received by the own station to the subsequent stations.  Setting parameters for this function is not required because the master station automatically sets the parameters according to the system configuration. |

| Multicast mode         | A communication mode used to send cyclic data to multiple stations                                                                                                                                                                                                                             |

| Offset binary          | Signed number representations. A method where a predetermined bias value is subtracted.                                                                                                                                                                                                        |

| Remote buffer memory   | Memory in an FPGA module for storing data such as setting values and monitored values                                                                                                                                                                                                          |

| Remote station         | A station that exchanges I/O signals (bit data) and I/O data (word data) with another station by cyclic transmission.  This station can perform transient transmission.                                                                                                                        |

| Reserved station       | A station reserved for future use. This station is not actually connected, but counted as a connected station.                                                                                                                                                                                 |

| Sample circuit         | A connection example of the user circuit and the standard circuits. The sample circuit is incorporated in the FPGA module of factory default.                                                                                                                                                  |

| SLMP                   | An abbreviation for Seamless Message Protocol. This protocol is used for Ethernet.                                                                                                                                                                                                             |

| Standard circuit       | A circuit block that controls the external hardware (digital I/O circuits, analog circuits) of the FPGA. The standard circuit is provided by Mitsubishi Electric Corporation and the circuit change by users is not required.                                                                  |

| Transient transmission | A function of communication with another station, which is used when requested by a dedicated instruction or an engineering tool                                                                                                                                                               |

| TSN hub                | A CC-Link IE TSN Class B switching hub authorized by the CC-Link Partner Association                                                                                                                                                                                                           |

| User circuit           | A circuit block that is designed by a user according to the application.                                                                                                                                                                                                                       |

| Verilog                | A hardware description language (HDL) used to describe digital circuits                                                                                                                                                                                                                        |

<sup>\*1</sup> The term has been changed for standardization among manuals and software applications related to CC-Link IE TSN. However, the term used in some CC-Link IE TSN related software windows may remain unchanged and may be different from the term used in this manual.

In case of inconsistency, refer to the following.

| Term used in software window | Term after change    |

|------------------------------|----------------------|

| Authentication Class         | CC-Link IE TSN Class |

## **GENERIC TERMS AND ABBREVIATIONS**

Unless otherwise specified, this manual uses the following generic terms and abbreviations.

| Generic term/abbreviation | Description                                                                                                                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC                       | An abbreviation for an A/D converter. The analog input part of the standard circuit controls it.                                                                                                      |

| DAC                       | An abbreviation for a D/A converter. The analog output part of the standard circuit controls it.                                                                                                      |

| FPGA module               | An abbreviation for the CC-Link IE TSN FPGA module. A generic term for a main module and an extension module.                                                                                         |

| H/W                       | An abbreviation for hardware                                                                                                                                                                          |

| REMFR                     | A generic term for the JP.REMFR and ZP.REMFR                                                                                                                                                          |

| REMFRD                    | An abbreviation for JP.REMFRD                                                                                                                                                                         |

| REMFRDIP                  | An abbreviation for GP.REMFRDIP                                                                                                                                                                       |

| REMFRIP                   | An abbreviation for GP.REMFRIP                                                                                                                                                                        |

| REMTO                     | A generic term for the JP.REMTO and ZP.REMTO                                                                                                                                                          |

| REMTOD                    | An abbreviation for JP.REMTOD                                                                                                                                                                         |

| REMTODIP                  | An abbreviation for GP.REMTODIP                                                                                                                                                                       |

| REMTOIP                   | An abbreviation for GP.REMTOIP                                                                                                                                                                        |

| RWr                       | An abbreviation for a remote register of a link device. Word data input from a device station to the master station. (For some areas in a local station, data are input in the opposite direction.)   |

| RWw                       | An abbreviation for a remote register of a link device. Word data output from the master station to a device station. (For some areas in a local station, data are output in the opposite direction.) |

| RX                        | An abbreviation for remote input of a link device. Bit data input from a device station to the master station. (For some areas in a local station, data are input in the opposite direction.)         |

| RY                        | An abbreviation for remote output of a link device. Bit data output from the master station to a device station. (For some areas in a local station, data are output in the opposite direction.)      |

| S/W                       | An abbreviation for software                                                                                                                                                                          |

| SLMPSND                   | A generic term for the J.SLMPSND, JP.SLMPSND, G.SLMPSND, and GP.SLMPSND                                                                                                                               |

## PART 1

## **OVERVIEW**

This part consists of the following chapters.

1 WHAT THIS MODULE CAN DO

2 PRODUCT LINEUP

3 SYSTEM CONFIGURATION

## 1 WHAT THIS MODULE CAN DO

The FPGA module has the following features.

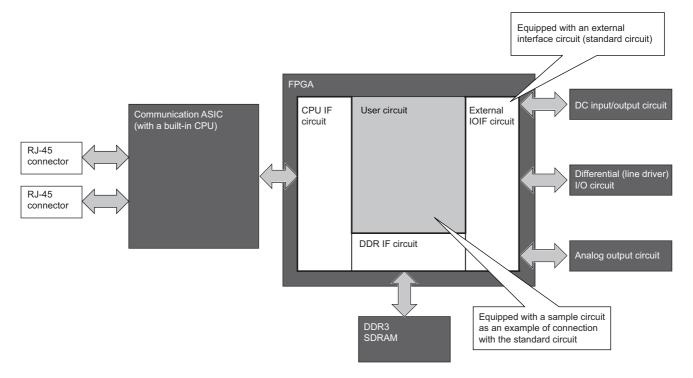

### No interface circuit design or verification required

Since the FPGA module is equipped with the standard circuit, users can focus on designing and verifying the user circuit. In addition, the user circuit includes sample circuits which can be used as an example of the standard circuit connection, and this reduces the working hours required for FPGA development.

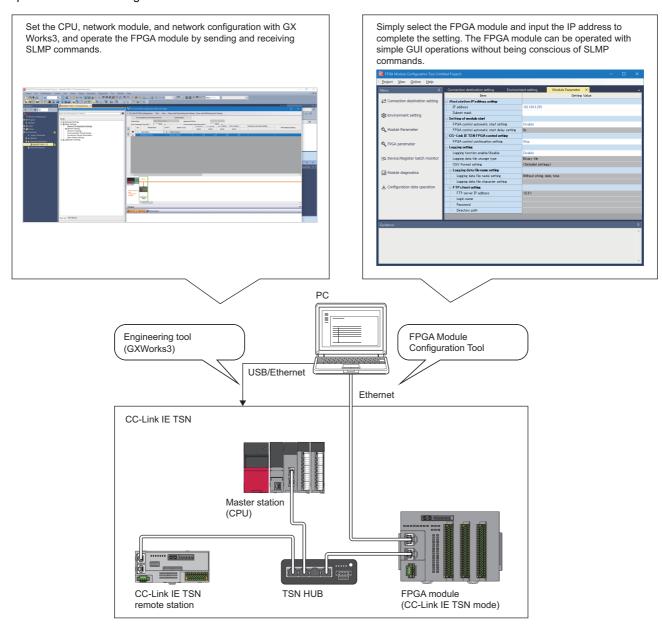

### Can be operated without GX Works3

Since the FPGA Module Configuration Tool can be connected to the FPGA module standalone, the FPGA module can be operated without GX Works3.

When using the FPGA Module Configuration Tool, the initial settings required for operating the FPGA module are only selection of an FPGA module and input of the IP address. In addition, the FPGA module can be operated with only simple operations without being conscious of SLMP commands.

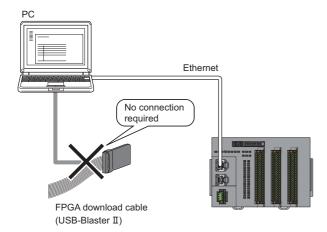

### Configuration data can be written to the FPGA module

The configuration data created with the FPGA development software can be written to the FPGA module by using the FPGA Module Configuration Tool. The user circuit can be updated via the network without reconnecting to the dedicated FPGA download cable. Also, the user circuit can be initialized by writing a sample circuit.

## 2 PRODUCT LINEUP

## 2.1 List of Products

### Main module

| Module name                                                                                      | Model name      | Connection circuit board                                                          | Reference                                                                                |

|--------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| CC-Link IE TSN FPGA module, DC input/output 96-point type                                        | NZ2GN2S-D41P01  | B0, B1, B2: DC input/output circuit board                                         | Page 34 NZ2GN2S-D41P01, DC input/<br>output: 96 points                                   |

| CC-Link IE TSN FPGA module, differential input/output 51-point type                              | NZ2GN2S-D41D01  | B0, B1, B2: Differential input/<br>output circuit board                           | Page 36 NZ2GN2S-D41D01,<br>differential input/output: 51 points                          |

| CC-Link IE TSN FPGA module, DC input/output 64-<br>point/differential input/output 17-point type | NZ2GN2S-D41PD02 | B0, B1: DC input/output circuit board B2: Differential input/output circuit board | Page 38 NZ2GN2S-D41PD02, DC input/output: 64 points/differential input/output: 17 points |

### **Extension module**

| Module name                                                                   | Model name     | Connection circuit board                                | Reference                                                       |

|-------------------------------------------------------------------------------|----------------|---------------------------------------------------------|-----------------------------------------------------------------|

| CC-Link IE TSN extension FPGA module, DC input/output 96-point type           | NZ2EX2S-D41P01 | E0, E1, E2: DC input/output circuit board               | Page 41 NZ2EX2S-D41P01, DC input/output: 96 points              |

| CC-Link IE TSN extension FPGA module, differential input/output 51-point type | NZ2EX2S-D41D01 | E0, E1, E2: Differential input/<br>output circuit board | Page 43 NZ2EX2S-D41D01,<br>differential input/output: 51 points |

| CC-Link IE TSN extension FPGA module, analog input/output 42-point type       | NZ2EX2S-D41A01 | E0, E1, E2: Analog input/output circuit board           | Page 46 NZ2EX2S-D41A01, analog input/output: 42 points          |

## **MEMO**

## 3 SYSTEM CONFIGURATION

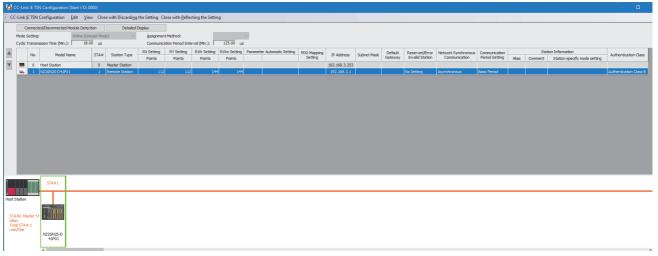

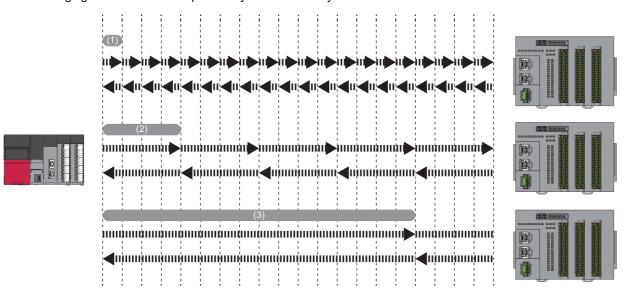

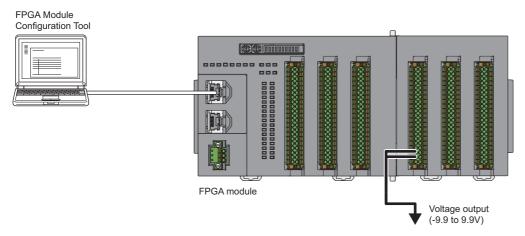

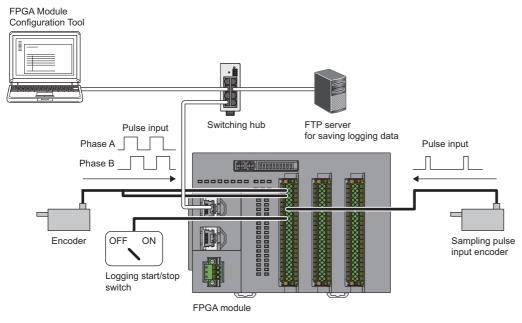

The FPGA module has the following two modes. An image of the system configuration to be used in each mode is shown.

- · Standalone mode

- · CC-Link IE TSN communication mode

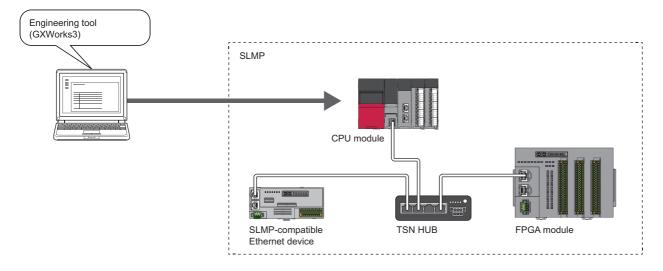

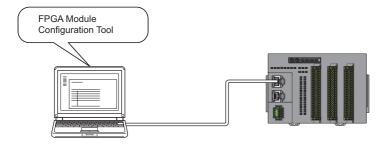

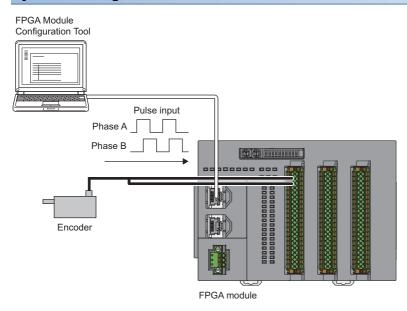

### System configuration in standalone mode

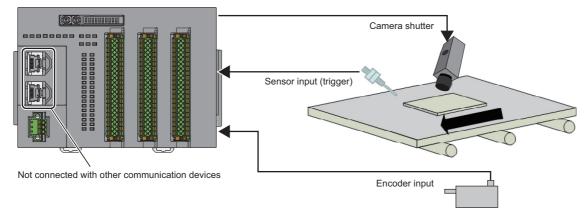

In standalone mode, the system can be controlled only by the FPGA module by setting parameters in advance using the FPGA Module Configuration Tool.

Also, in standalone mode, by connecting an SLMP-compatible device, the operation of the FPGA module can be controlled by SLMP commands.

When controlling the FPGA module using the CPU module, the simple CPU communication function can be used to send and receive SLMP commands to and from the FPGA module. For details on SLMP commands, refer to the following.

Page 351 SLMP Communication Function

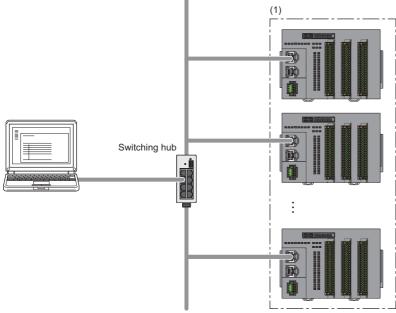

#### ■Network configuration in standalone mode

The star connection is the only connection method that can be used in standalone mode.

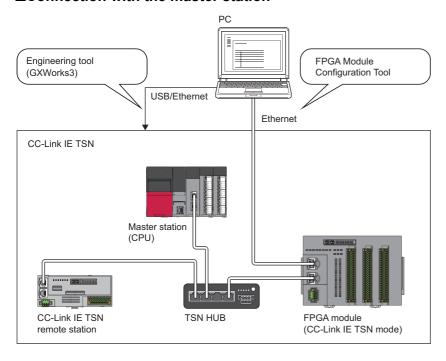

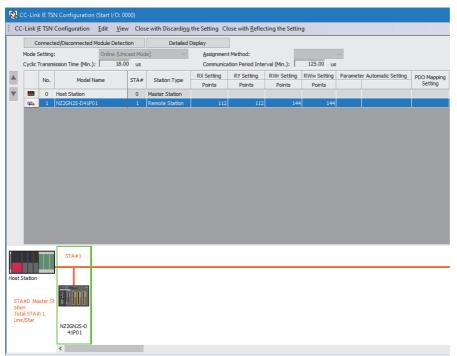

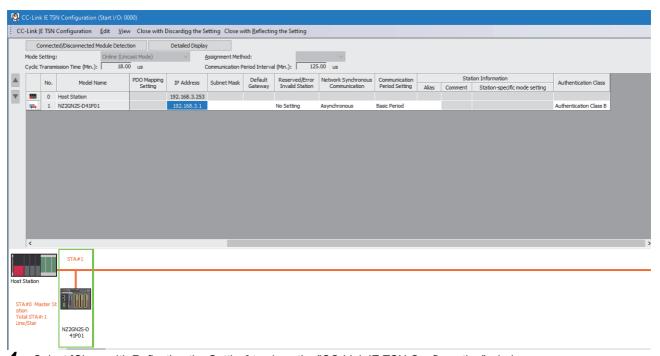

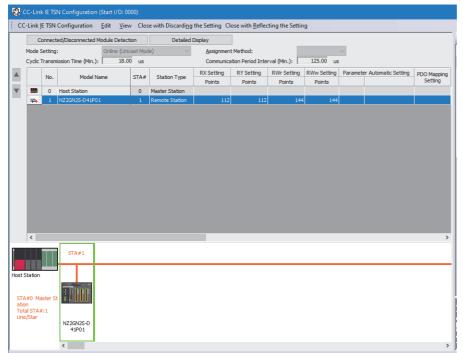

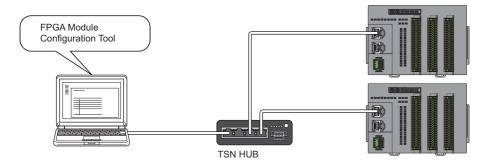

### **CC-Link IE TSN communication mode**

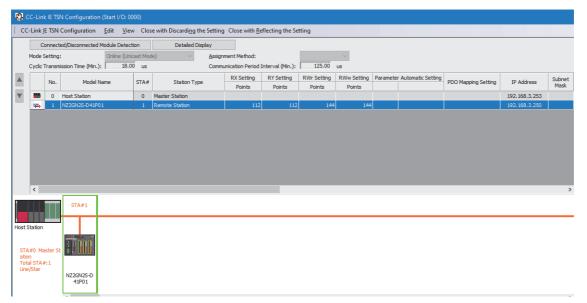

In CC-Link IE TSN communication mode, the FPGA module operates as a CC-Link IE TSN remote station.

#### **■**Connection with the master station

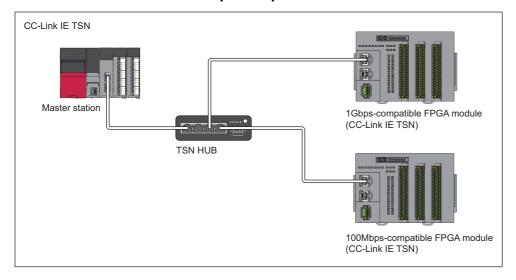

### **■**Connection when 1G/100Mbps compatible CC-Link IE TSN devices are mixed

For connection when devices with different communication speeds or CC-Link IE TSN Classes are mixed, refer to the manual for the master module being used.

### ■Network configuration in CC-Link IE TSN communication mode

The connection methods that can be used in CC-Link IE TSN communication mode are shown below.

- · Line topology

- Ring topology

- Star topology

- · Mixture of line topology and star topology

- The ring topology can only be connected when the CC-Link IE TSN Class is CC-Link IE TSN Class B. When a CC-Link IE TSN Class A FPGA module is connected by ring topology, data links are not established.

- In the ring topology, logging data cannot be transferred to the FTP server, so the logging function cannot be used.

## 3.1 Applicable Systems

#### Supported master station

When using the FPGA module in CC-Link IE TSN communication mode, use the following products for the master station.

| Model name                                | Firmware version |

|-------------------------------------------|------------------|

| RJ71GN11-T2                               | No restriction   |

| RD78G64, RD78G32, RD78G16, RD78G8, RD78G4 |                  |

| RD78GHV, RD78GHW                          | "05" or later    |

Information on "Supported master station" described above is the ones at the point when this manual was issued.

For latest information, please visit the website of CC-Link Partner Association.

www.cc-link.org

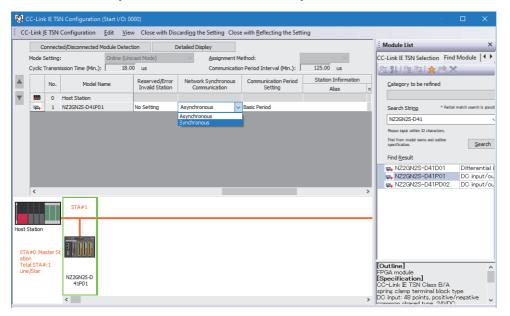

### Compatible software package

The table below lists the software packages compatible with the FPGA module.

| Product name                   | Software version |

|--------------------------------|------------------|

| GX Works3                      | 1.095Z or later  |

| FPGA Module Configuration Tool | No restriction   |

For the FPGA Module Configuration Tool, please consult your local Mitsubishi representative.

#### **FPGA** development software

The table below lists FPGA development software that are used for FPGA design and whose operation has been verified.

| Product name                     | Edition             | Software version |  |

|----------------------------------|---------------------|------------------|--|

| Intel <sup>®</sup> Quartus Prime | Lite Edition (free) | 20.1.1           |  |

|                                  | Standard Edition    | 20.1.1           |  |

For Intel® Quartus Prime, download it from the website below.

www.intel.com

#### Applicable profile

When the latest profile of the FPGA module is necessary, please consult your local Mitsubishi representative.

The profile is a setting file that stores information required for the start-up, operation, and maintenance of devices supporting the CC-Link family.

A module is added to "Module List" of the "CC-Link IE TSN Configuration" window by profile registration to the engineering tool of the master station.

For the profile registration, refer to the following.

GX Works3 Operating Manual

#### **Ethernet cables**

For the specifications of the Ethernet cable, refer to the following.

User's manual for the master station used

#### Switching hub

For compatible switching hubs, refer to the following.

User's manual for the master station used

## PART 2

## **SPECIFICATIONS**

This part consists of the following chapters.

4 PART NAMES

**5 SPECIFICATIONS**

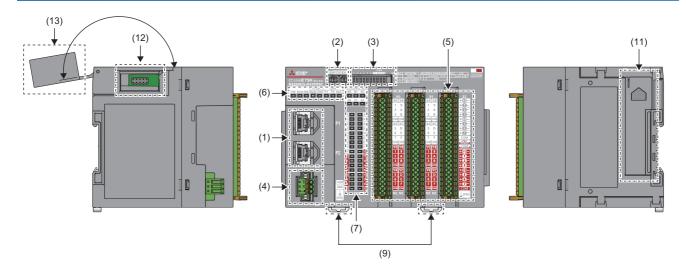

## 4 PART NAMES

This chapter describes the part names of the FPGA module.

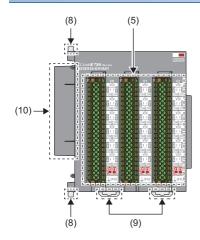

### Main module

### **Extension module**

| No. | Name                                          | Description                                                                                                                                                                                                                                          |

|-----|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

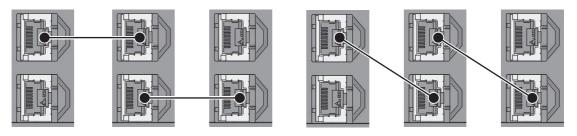

| (1) | P1                                            | A port for the connection to a network. (RJ45 connector)  Connects an Ethernet cable. (Fig. Page 68 Ethernet cables)  There are no restrictions on the connection order of the cables for P1 and P2.  The LEDs of the Ethernet ports are always off. |

|     | P2                                            | Same as P1                                                                                                                                                                                                                                           |

| (2) | IP address/station number setting switch      | Sets the IP address fourth octet. ( Page 54 IP address/station number setting switch setting)                                                                                                                                                        |

| (3) | Function setting switch                       | Sets the operation mode and the communication speed. ( Page 58 Setting the function setting switches)                                                                                                                                                |

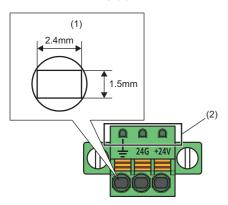

| (4) | Terminal block for module power supply and FG | A terminal block for the connection to module power supply (24VDC) and FG. (Fig. Page 66 Wiring to terminal block for module power supply and FG)                                                                                                    |

| (5) | I/O terminal block                            | A terminal block for the connection to external devices. ( 🖙 Page 70 Wiring to I/O terminal block)                                                                                                                                                   |

| No.  | Name                      | Description                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| (6)  | PW LED                    | Indicates the power supply status of the FPGA module.  On: Power supply ON  Off: Power supply OFF                                                                                                                                                                                                              |  |  |  |  |  |

|      | RUN LED                   | Indicates the operating status of the FPGA module.  On: Operating normally  Flashing: Operating in unit test mode, updating the firmware, or initializing the stand-alone mode IP address  Off: A major error has occurred, firmware update completed, or stand-alone mode IP address initialization completed |  |  |  |  |  |

|      | ERR. LED                  | Indicates the error status of the FPGA module.  On: A moderate error or major error has occurred  Flashing: A minor error has occurred  Off: Operating normally                                                                                                                                                |  |  |  |  |  |

|      | FPGA RUN LED              | Indicates the execution status of the FPGA control.  On: FPGA control being executed  Off: FPGA control stopped                                                                                                                                                                                                |  |  |  |  |  |

|      | FPGA CONF. LED            | Indicates the FPGA configuration status.  On: Configuration completed successfully Flashing: FPGA download being executed Off: Configuration incomplete or configuration error                                                                                                                                 |  |  |  |  |  |

|      | P1 LINK LED               | Indicates the link status for PORT1.  • On: Link-up  • Off: Link-down                                                                                                                                                                                                                                          |  |  |  |  |  |

|      | P2 LINK LED               | Indicates the link status for PORT2.  On: Link-up  Off: Link-down                                                                                                                                                                                                                                              |  |  |  |  |  |

|      | DATA LINK LED             | Indicates the data link status of the FPGA module during CC-Link IE TSN communications.  On: Cyclic transmission being performed  Flashing: Cyclic transmission stopped  Off: Cyclic transmission not performed, own station disconnected, or operating in stand-alone mode                                    |  |  |  |  |  |

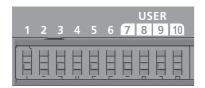

| (7)  | TERMINAL NO.              | Indicates the terminal block whose I/O status is to be displayed.                                                                                                                                                                                                                                              |  |  |  |  |  |

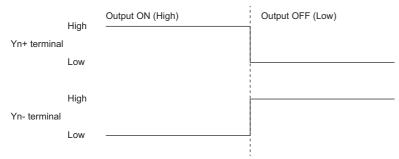

|      | X0 LED to XF LED          | ■DC I/O terminal block Indicates the ON/OFF status of the inputs.  • On: Input ON  • Off: Input OFF ■Differential I/O terminal block*1*2 Indicates the ON/OFF status of the inputs.*3  • On: Input ON  • Off: Input OFF ■Analog I/O terminal block*4 No indication                                             |  |  |  |  |  |

|      | XY LED*5                  | ■DC I/O terminal block Always off ■Differential I/O terminal block*1*2 Indicates the ON/OFF status of the XY terminal.*3 • On: XY terminal ON • Off: XY terminal OFF ■Analog I/O terminal block*4 No indication                                                                                                |  |  |  |  |  |

|      | Y0 LED to YF LED*5        | ■DC I/O terminal block Indicates the ON/OFF status of the outputs.  • On: Output ON  • Off: Output OFF ■Differential I/O terminal block*1*2 Indicates the ON/OFF status of the outputs.  • On: Output ON  • Off: Output OFF ■Analog I/O terminal block*4 No indication                                         |  |  |  |  |  |

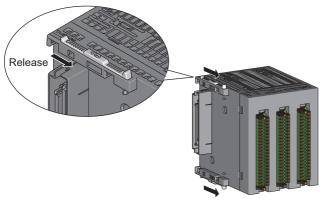

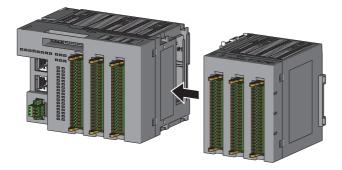

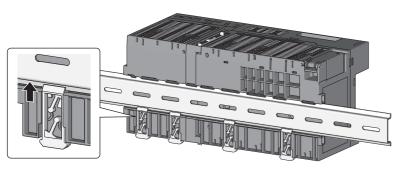

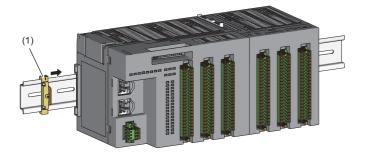

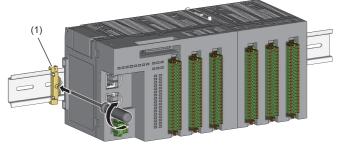

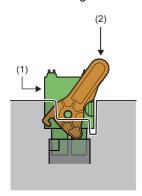

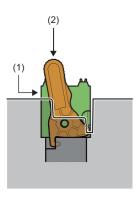

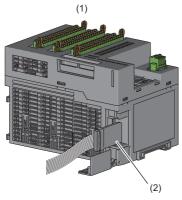

| (8)  | Module joint lever        | A lever to fix the connected part of the modules when connecting an extension module to the main module. (Fig. Page 61 Connecting an extension module)                                                                                                                                                         |  |  |  |  |  |

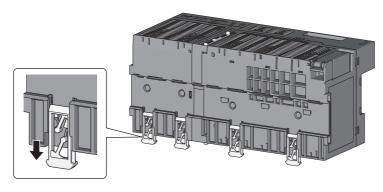

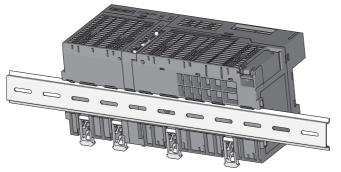

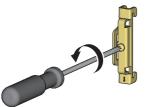

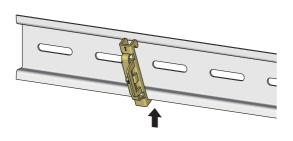

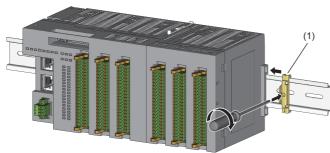

| (9)  | DIN rail hook             | A hook to mount the FPGA module on a DIN rail                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| (10) | Extension connector       | A connector to connect an extension module to the main module                                                                                                                                                                                                                                                  |  |  |  |  |  |

| (11) | Extension connector cover | A cover to protect a connector of an extension module. (Fig. Page 61 Connecting an extension module)                                                                                                                                                                                                           |  |  |  |  |  |

| (12) | JTAG connector            | Used for writing configuration data to the FPGA module via JTAG. (FP Page 300 FPGA Download Function)                                                                                                                                                                                                          |  |  |  |  |  |

| (13) | JTAG connector cover      | A protective cover for the JTAG connector                                                                                                                                                                                                                                                                      |  |  |  |  |  |

- \*1 The LEDs indicate the ON/OFF status of differential I/O positive (+) signals.

- \*2 The differential I/O terminal block has 8 points of X terminals and 8 points of Y terminals, and thus X8 to XF LEDs and Y8 to YF LEDs are always off.

- \*3 Depending on whether the XY terminal is used as an input terminal or an output terminal, the LED that indicates the ON/OFF status varies. When the XY terminal is used as an input terminal, the XY LED on the left indicates the ON/OFF status of the input. When the XY terminal is used as an output terminal, the XY LED on the right indicates the ON/OFF status of the output. For input/output selection of the XY terminal, refer to the following register.

- · Output signal/Input output direction signal selection (B0) (ioport\_iob0\_dio485\_osel)

- · Output value/Input output direction setting (B0) (ioport\_iob0\_dio485\_odata)

- \*4 For the analog I/O terminal block, the TERMINAL NO. LEDs do not turn on.

- \*5 The ON/OFF conditions of the output signals vary depending on the settings of Output signal selection ((B0) (oport\_iob0y\_osel) to (E2) (oport\_ioe2y\_osel)) and Output value/Input output direction setting ((B0) (ioport\_iob0\_dio485\_odata) to (E2) (ioport\_ioe2\_dio485\_osel)). The ON/OFF conditions of each setting are as follows.

- · Register circuit output is selected: Remote output signal (RY)

- · User circuit output is selected: User circuit output signal

#### Module status and LED status in CC-Link IE TSN communication mode

| FPGA module status      |                                        | LED status |          |          |                 |                   |                  |